# **CPB906**

Vortex86DX Based COM Module

# **User Manual**

Rev. 001 E November 2010

PRELIMINARY

Product Title: CPB906 Document name: CPB906 User Manual Manual version: 001 E Ref. doc. ver.: 1.0 R (ИМЕС.421459.906 РЭ)

Copyright © 2010 Fastwel Co. Ltd. All rights reserved.

#### **Revision Record**

| Rev. Index | Brief Description of Changes | Board Index | Date of Issue |

|------------|------------------------------|-------------|---------------|

| 001        | Initial version              | CPB906      | November 2010 |

|            |                              |             |               |

#### **Contact Information**

|          | Fastwel Co. Ltd                                                |            | Fastwel Corporation US                                       |

|----------|----------------------------------------------------------------|------------|--------------------------------------------------------------|

| Address: | 108 Profsoyuznaya st.,<br>Moscow 117437,<br>Russian Federation |            | 45 Main Street, Suite 319<br>Brooklyn, New York 11201<br>USA |

| Tel.:    | +7 (495) 232-1681                                              |            | +1 (718) 554-3686                                            |

| Fax:     | +7 (495) 232-1654                                              |            | +1 (718) 797-0600                                            |

|          |                                                                | Toll free: | +1 (877) 787-8443 (1-877-RURUGGED)                           |

| E-mail:  | info@fastwel.com                                               |            |                                                              |

| Web:     | http://www.fastwel.com/                                        |            |                                                              |

# **Table of Contents**

|   | Table  | e of Conte       | ents                                                          | 1  |

|---|--------|------------------|---------------------------------------------------------------|----|

|   |        |                  |                                                               |    |

|   | List c | of Figures.      |                                                               | 3  |

|   | Nota   | tion Conve       | entions                                                       | 4  |

|   | Gene   | eral Safety      | y Precautions                                                 | 5  |

|   | Unpa   | acking, Ins      | spection and Handling                                         | 6  |

|   | Three  | e Year Wa        | arranty                                                       | 7  |

| 1 | Intro  | oduction         | 1                                                             |    |

|   | 1.1    | Module           | Introduction                                                  | 8  |

|   | 1.2    | Main Sp          | pecifications                                                 | 8  |

|   | 1.3    | Functio          | nal Diagram                                                   | 11 |

|   | 1.4    | Appeara          | ance and Layout                                               | 12 |

|   | 1.5    | CPB906           | 6 Versions                                                    | 13 |

|   | 1.6    | Delivery         | y Checklist                                                   | 13 |

|   | 1.7    | Addition         | nal Accessories                                               | 14 |

|   | 1.8    | Functio          | onal Description                                              | 14 |

|   |        | 1.8.1            | Vortex86DX SoC                                                | 14 |

|   |        | 1.8.2            | XS1 Main High-Dencity Connector                               | 15 |

|   |        | 1.8.3            | Supervisor and Watchdog Timers                                | 19 |

|   |        |                  | 1.8.3.1 WDT0 and WDT1 Registers Description                   | 19 |

|   |        | 1.8.4            | SDRAM Memory                                                  |    |

|   |        | 1.8.5            | Flash BIOS                                                    |    |

|   |        | 1.8.6            | ATA Flash Disk                                                |    |

|   |        | 1.8.7            | IDE/SDIO Port                                                 |    |

|   |        | 1.8.8            | COM1, COM2 Serial Ports                                       |    |

|   |        | 1.8.9            | PS/2 Keyboard and Mouse Interface                             |    |

|   |        | 1.8.10           | RTC and Battery                                               |    |

|   |        | 1.8.11           | USB Interface                                                 |    |

|   |        | 1.8.12           | Fast Ethernet Interface                                       |    |

|   |        | 1.8.13           | FRAM                                                          |    |

|   |        | 1.8.14           | Remote Reset/Interrupt, Remote Power Fail Signal Source Ports |    |

|   |        | 1.8.15           | 8-bit ISA Port                                                |    |

|   |        | 1.8.16           | LPC Port.                                                     | -  |

|   |        | 1.8.17           | PCI Port (XS1)                                                |    |

|   |        | 1.8.18           | I2C Port                                                      |    |

|   |        | 1.8.19           | GPIO Port                                                     |    |

|   |        | 1.8.20<br>1.8.21 | PC-Buzzer Port                                                |    |

|   |        | 1.8.22           | LED indicators<br>Redundancy Port                             |    |

| _ |        |                  |                                                               |    |

| 2 |        |                  | formation                                                     |    |

|   | 2.1    |                  | are Interrupts                                                |    |

|   | 2.2    |                  | hannels                                                       |    |

|   | 2.3    |                  |                                                               |    |

|   | 2.4    | •                | y Addressing                                                  |    |

|   | 2.5    |                  | Processor Ports                                               |    |

|   | 2.6    | Overall          | and Mounting Dimensions                                       |    |

| 3 | Syst | tem Set | up                               |    |

|---|------|---------|----------------------------------|----|

|   | 3.1  | Safety  | Regulations                      |    |

|   | 3.2  | Jumpe   | er Settings                      |    |

|   | 3.3  | Softwa  | are Installation                 |    |

|   | 3.4  | AMI BI  | IOS                              |    |

|   |      | 3.4.1   | BIOS Setup Program. Introduction |    |

|   | 3.5  | Basic S | Software                         | 35 |

|   | 3.6  | Service | e Software                       | 35 |

|   |      | 3.6.1   | SPIFLASH.EXE Utility             | 35 |

|   | 3.7  | CPB90   | 06 Programming FAQ               | 35 |

| 4 | Арр  | endices | 5                                |    |

|   | 4.1  | KIB880  | 0 Carrier Board                  |    |

|   |      | 4.1.1   | Introduction                     |    |

|   |      | 4.1.2   | Appearance and Layout            |    |

|   |      | 4.1.3   | Functional Diagram               |    |

|   |      | 4.1.4   | Specifications                   |    |

|   |      | 4.1.5   | Delivery Checklist               | 41 |

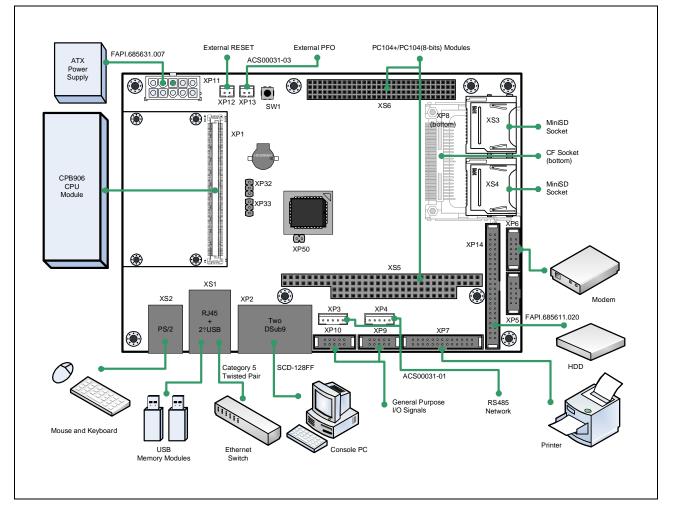

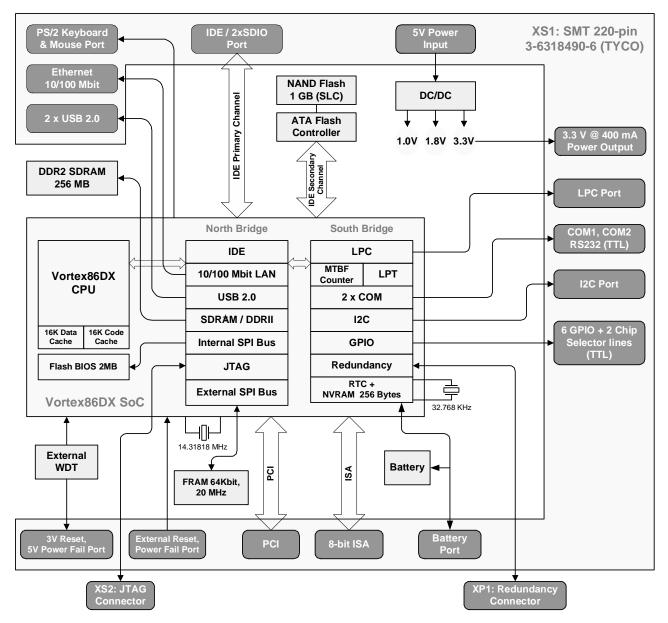

|   |      | 4.1.6   | External Connections             | 41 |

|   |      |         |                                  |    |

# List of Tables

| Table 1.2:CPB906 Additional AccessoriesTable 1.3:XS1: Main High-Density Connector PinoutTable 1.3:WDT0 Restart RegisterTable 1.5:WDT0 Port Address Index RegisterTable 1.6:WDT0 Port Data RegisterTable 1.7:WDT0 Timer Control RegisterTable 1.8:WDT0 Event Selection RegisterTable 1.9:WDT0 Timer Value CNT0 RegisterTable 1.10:WDT0 Timer Value CNT1 RegisterTable 1.11:WDT0 Timer Value CNT2 RegisterTable 1.12:WDT0 Timer Value CNT2 RegisterTable 1.13:WDT1 Timer Control RegisterTable 1.14:WDT0 Timer Value CNT2 RegisterTable 1.15:WDT1 Timer Control RegisterTable 1.16:WDT1 Timer Control RegisterTable 1.17:WDT1 Timer Control RegisterTable 1.16:WDT1 Timer Value CNT2 RegisterTable 1.17:WDT1 Timer Value CNT2 RegisterTable 1.18:WDT1 Timer Value CNT0 RegisterTable 1.19:WDT1 Timer Value CNT2 RegisterTable 1.16:WDT1 Timer Value CNT2 RegisterTable 1.17:WDT1 Timer Value CNT2 RegisterTable 1.18:WDT1 Timer Value CNT2 RegisterTable 1.19:WDT1 Timer Value CNT2 RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED Indicators.Table 1.22:XP1 Redundancy Connector PinoutTable 1.22:XP1 Redundancy Connector PinoutTable 2.21:Interrupt Settings.Table 2.31:I/O Address SpaceTable 2.4:Memory Address Mapping | Table 1.1:  | CPB906 Versions                           | .13 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------|-----|

| Table 1.4:WDT0 Restart RegisterTable 1.5:WDT0 Port Address Index RegisterTable 1.6:WDT0 Port Data RegisterTable 1.7:WDT0 Timer Control RegisterTable 1.8:WDT0 Event Selection RegisterTable 1.9:WDT0 Timer Value CNT0 RegisterTable 1.10:WDT0 Timer Value CNT1 RegisterTable 1.11:WDT0 Timer Value CNT2 RegisterTable 1.12:WDT0 Timer Value CNT2 RegisterTable 1.13:WDT1 Timer Control RegisterTable 1.14:WDT1 Timer Control RegisterTable 1.15:WDT1 Timer Control RegisterTable 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT0 RegisterTable 1.18:WDT1 Timer Value CNT0 RegisterTable 1.18:WDT1 Timer Value CNT1 RegisterTable 1.19:WDT1 Timer Value CNT2 RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED IndicatorsTable 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt SettingsTable 2.3:I/O Address MappingTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                     | Table 1.2:  | CPB906 Additional Accessories             | .14 |

| Table 1.5:WDT0 Port Address Index Register.Table 1.6:WDT0 Port Data Register.Table 1.7:WDT0 Timer Control RegisterTable 1.8:WDT0 Event Selection RegisterTable 1.9:WDT0 Timer Value CNT0 RegisterTable 1.10:WDT0 Timer Value CNT1 RegisterTable 1.11:WDT0 Timer Value CNT2 RegisterTable 1.12:WDT0 Timer Value CNT2 RegisterTable 1.13:WDT1 Restart RegisterTable 1.14:WDT1 Timer Control RegisterTable 1.15:WDT1 Timer Control RegisterTable 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT0 RegisterTable 1.18:WDT1 Timer Value CNT0 RegisterTable 1.18:WDT1 Timer Value CNT2 RegisterTable 1.19:WDT1 Timer Value CNT2 RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED Indicators.Table 1.22:XP1 Redundancy Connector PinoutTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control RegistersTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                | Table 1.3:  | XS1: Main High-Density Connector Pinout   | .15 |

| Table 1.6:WDT0 Port Data RegisterTable 1.7:WDT0 Timer Control RegisterTable 1.8:WDT0 Event Selection RegisterTable 1.9:WDT0 Timer Value CNT0 RegisterTable 1.10:WDT0 Timer Value CNT1 RegisterTable 1.11:WDT0 Timer Value CNT2 RegisterTable 1.12:WDT0 Timer Value CNT2 RegisterTable 1.13:WDT1 Restart RegisterTable 1.14:WDT1 Timer Control RegisterTable 1.15:WDT1 Event Selection RegisterTable 1.16:WDT1 Timer Value CNT2 RegisterTable 1.17:WDT1 Timer Control RegisterTable 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT1 RegisterTable 1.18:WDT1 Timer Value CNT1 RegisterTable 1.19:WDT1 Timer Value CNT2 RegisterTable 1.19:WDT1 Timer Value CNT2 RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED Indicators.Table 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt Settings.Table 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address Mapping.Table 2.5:Processor GPIO Control Registers.Table 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                 | Table 1.4:  | WDT0 Restart Register                     | .19 |

| Table 1.7:WDT0 Timer Control RegisterTable 1.8:WDT0 Event Selection RegisterTable 1.9:WDT0 Timer Value CNT0 RegisterTable 1.10:WDT0 Timer Value CNT1 RegisterTable 1.11:WDT0 Timer Value CNT2 RegisterTable 1.12:WDT0 Timer Value CNT2 RegisterTable 1.13:WDT1 Restart RegisterTable 1.14:WDT1 Timer Control RegisterTable 1.15:WDT1 Timer Control RegisterTable 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT0 RegisterTable 1.18:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT0 RegisterTable 1.18:WDT1 Timer Value CNT0 RegisterTable 1.19:WDT1 Timer Value CNT0 RegisterTable 1.19:WDT1 Timer Value CNT0 RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED Indicators.Table 1.22:XP1 Redundancy Connector PinoutTable 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control RegistersTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                | Table 1.5:  | WDT0 Port Address Index Register          | .19 |

| Table 1.8:WDT0 Event Selection RegisterTable 1.9:WDT0 Timer Value CNT0 RegisterTable 1.10:WDT0 Timer Value CNT1 RegisterTable 1.11:WDT0 Timer Value CNT2 RegisterTable 1.12:WDT0 Timer Mode RegisterTable 1.13:WDT1 Restart RegisterTable 1.14:WDT1 Timer Control RegisterTable 1.15:WDT1 Event Selection RegisterTable 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT0 RegisterTable 1.18:WDT1 Timer Value CNT0 RegisterTable 1.19:WDT1 Timer Value CNT2 RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED Indicators.Table 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt Settings.Table 2.3:I/O Address SpaceTable 2.4:Memory Address Mapping.Table 2.5:Processor GPIO Control Registers.Table 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Table 1.6:  | WDT0 Port Data Register                   | .19 |

| Table 1.9:WDT0 Timer Value CNT0 Register2Table 1.10:WDT0 Timer Value CNT1 Register2Table 1.11:WDT0 Timer Value CNT2 Register2Table 1.12:WDT0 Timer Mode Register2Table 1.13:WDT1 Restart Register2Table 1.14:WDT1 Timer Control Register2Table 1.15:WDT1 Event Selection Register2Table 1.16:WDT1 Timer Value CNT0 Register2Table 1.17:WDT1 Timer Value CNT0 Register2Table 1.18:WDT1 Timer Value CNT0 Register2Table 1.19:WDT1 Timer Value CNT2 Register2Table 1.20:Frequency Divider Values for Serial Ports2Table 1.21:LED Indicators.2Table 1.22:XP1 Redundancy Connector Pinout2Table 2.1:Interrupt Settings2Table 2.3:I/O Address Space2Table 2.4:Memory Address Mapping2Table 2.5:Processor GPIO Control Registers.2Table 2.6:Processor GPIO Lines Description2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Table 1.7:  | WDT0 Timer Control Register               | .20 |

| Table 1.10:WDT0 Timer Value CNT1 RegisterTable 1.11:WDT0 Timer Value CNT2 RegisterTable 1.12:WDT0 Timer Mode RegisterTable 1.13:WDT1 Restart RegisterTable 1.14:WDT1 Timer Control RegisterTable 1.15:WDT1 Event Selection RegisterTable 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT0 RegisterTable 1.18:WDT1 Timer Value CNT1 RegisterTable 1.19:WDT1 Timer Value CNT2 RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED Indicators.Table 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt SettingsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table 1.8:  |                                           |     |

| Table 1.11:WDT0 Timer Value CNT2 RegisterTable 1.12:WDT0 Timer Mode RegisterTable 1.13:WDT1 Restart RegisterTable 1.14:WDT1 Timer Control RegisterTable 1.15:WDT1 Event Selection RegisterTable 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT0 RegisterTable 1.18:WDT1 Timer Value CNT2 RegisterTable 1.19:WDT1 Timer Value CNT2 RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED IndicatorsTable 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Table 1.9:  | WDT0 Timer Value CNT0 Register            | .20 |

| Table 1.12:WDT0 Timer Mode RegisterTable 1.13:WDT1 Restart RegisterTable 1.14:WDT1 Timer Control RegisterTable 1.15:WDT1 Event Selection RegisterTable 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT1 RegisterTable 1.18:WDT1 Timer Value CNT2 RegisterTable 1.19:WDT1 Timer Mode RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED IndicatorsTable 2.1:Interrupt SettingsTable 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Table 1.10: | WDT0 Timer Value CNT1 Register            | .21 |

| Table 1.13:WDT1 Restart Register.Table 1.14:WDT1 Timer Control Register.Table 1.15:WDT1 Event Selection Register.Table 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT1 RegisterTable 1.18:WDT1 Timer Value CNT2 RegisterTable 1.19:WDT1 Timer Mode RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED Indicators.Table 2.1:Interrupt Settings.Table 2.2:DMA Channels.Table 2.3:I/O Address SpaceTable 2.4:Memory Address Mapping.Table 2.5:Processor GPIO Control Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 1.11: | WDT0 Timer Value CNT2 Register            | .21 |

| Table 1.14:WDT1 Timer Control RegisterTable 1.15:WDT1 Event Selection RegisterTable 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT1 RegisterTable 1.18:WDT1 Timer Value CNT2 RegisterTable 1.19:WDT1 Timer Value CNT2 RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED IndicatorsTable 2.1:Interrupt SettingsTable 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Table 1.12: | WDT0 Timer Mode Register                  | .21 |

| Table 1.15:WDT1 Event Selection RegisterTable 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT1 RegisterTable 1.18:WDT1 Timer Value CNT2 RegisterTable 1.19:WDT1 Timer Mode RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED IndicatorsTable 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt SettingsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control RegistersTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 1.13: | WDT1 Restart Register                     | .21 |

| Table 1.16:WDT1 Timer Value CNT0 RegisterTable 1.17:WDT1 Timer Value CNT1 RegisterTable 1.18:WDT1 Timer Value CNT2 RegisterTable 1.19:WDT1 Timer Mode RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED IndicatorsTable 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt SettingsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control RegistersTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Table 1.14: | WDT1 Timer Control Register               | .22 |

| Table 1.17:WDT1 Timer Value CNT1 RegisterTable 1.18:WDT1 Timer Value CNT2 RegisterTable 1.19:WDT1 Timer Mode RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED IndicatorsTable 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt SettingsTable 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control RegistersTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 1.15: | WDT1 Event Selection Register             | .22 |

| Table 1.18:WDT1 Timer Value CNT2 RegisterTable 1.19:WDT1 Timer Mode RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED IndicatorsTable 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt SettingsTable 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control RegistersTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 1.16: | WDT1 Timer Value CNT0 Register            | .22 |

| Table 1.19:WDT1 Timer Mode RegisterTable 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED Indicators.Table 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt Settings.Table 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address Mapping.Table 2.5:Processor GPIO Control Registers.Table 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table 1.17: | WDT1 Timer Value CNT1 Register            | .22 |

| Table 1.20:Frequency Divider Values for Serial PortsTable 1.21:LED Indicators.Table 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt Settings.Table 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address Mapping.Table 2.5:Processor GPIO Control Registers.Table 2.6:Processor GPIO Lines Description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 1.18: | WDT1 Timer Value CNT2 Register            | .23 |

| Table 1.21:LED Indicators.Table 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt Settings.Table 2.2:DMA Channels.Table 2.3:I/O Address SpaceTable 2.4:Memory Address Mapping.Table 2.5:Processor GPIO Control Registers.Table 2.6:Processor GPIO Lines Description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table 1.19: | WDT1 Timer Mode Register                  | .23 |

| Table 1.22:XP1 Redundancy Connector PinoutTable 2.1:Interrupt SettingsTable 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control RegistersTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 1.20: | Frequency Divider Values for Serial Ports | .25 |

| Table 2.1:Interrupt SettingsTable 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control RegistersTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table 1.21: | LED Indicators                            | .27 |

| Table 2.2:DMA ChannelsTable 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control RegistersTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 1.22: | XP1 Redundancy Connector Pinout           | .28 |

| Table 2.3:I/O Address SpaceTable 2.4:Memory Address MappingTable 2.5:Processor GPIO Control RegistersTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table 2.1:  | Interrupt Settings                        | .29 |

| Table 2.4:Memory Address MappingTable 2.5:Processor GPIO Control RegistersTable 2.6:Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 2.2:  |                                           | -   |

| Table 2.5:       Processor GPIO Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table 2.3:  | I/O Address Space                         | .30 |

| Table 2.6:     Processor GPIO Lines Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table 2.4:  | Memory Address Mapping                    | .31 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table 2.5:  | Processor GPIO Control Registers          | .31 |

| Table 3.1:   Jumper Positions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 2.6:  | Processor GPIO Lines Description          | .32 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table 3.1:  | Jumper Positions                          | .34 |

# **List of Figures**

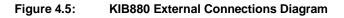

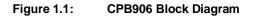

| Figure 1.1: | CPB906 Block Diagram                                                         | 11 |

|-------------|------------------------------------------------------------------------------|----|

| Figure 1.2: | CPB906 Module Appearance                                                     |    |

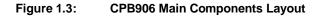

| Figure 1.3: | CPB906 Main Components Layout                                                | 12 |

| Figure 1.4: | XS1 Main High-Dencity Connector                                              |    |

| Figure 1.5: | Connection of CPB906 COM-Express Connector and the Carrier Board Counterpart |    |

| Figure 1.6: | Redundancy Connection                                                        | 28 |

| Figure 2.1: | CPB906: Overall and Mounting Dimensions                                      | 32 |

| Figure 4.1: | KIB880 Appearance                                                            | 36 |

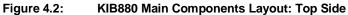

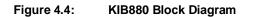

| Figure 4.2: | KIB880 Main Components Layout: Top Side                                      |    |

| Figure 4.3: | KIB880 Main Components Layout: Bottom Side                                   | 38 |

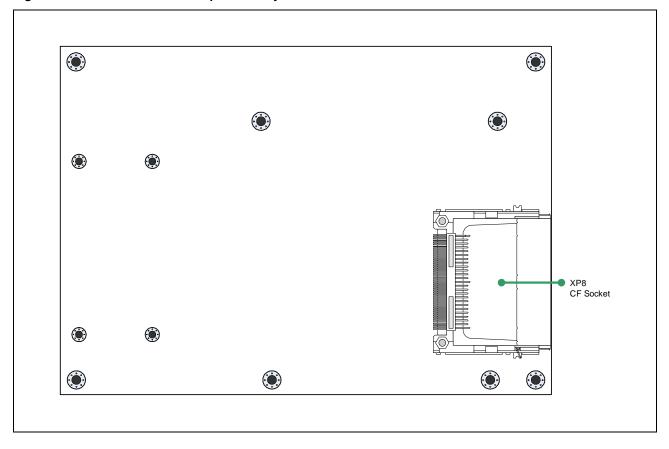

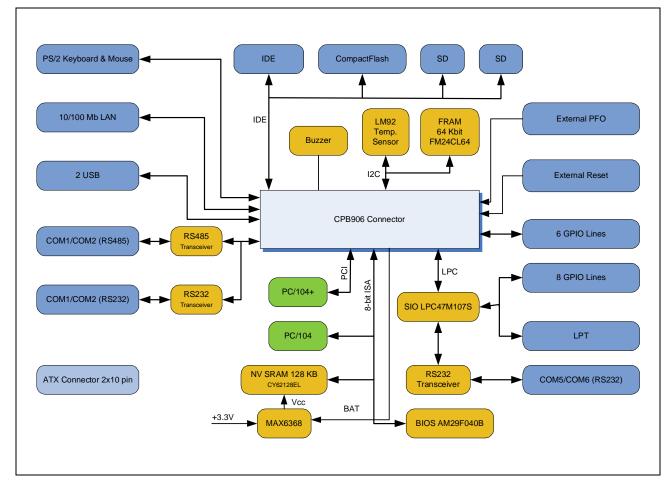

| Figure 4.4: | KIB880 Block Diagram                                                         |    |

| Figure 4.5: | KIB880 External Connections Diagram                                          |    |

All information in this document is provided for reference only, with no warranty of its suitability for any specific purpose. This information has been thoroughly checked and is believed to be entirely reliable and consistent with the product that it describes. However, Fastwel accepts no responsibility for inaccuracies, omissions or their consequences, as well as liability arising from the use or application of any product or example described in this document.

Fastwel Co. Ltd. reserves the right to change, modify, and improve this document or the products described in it, at Fastwel's discretion without further notice. Software described in this document is provided on an "as is" basis without warranty. Fastwel assumes no liability for consequential or incidental damages originated by the use of this software.

This document contains information, which is property of Fastwel Co. Ltd. It is not allowed to reproduce it or transmit by any means, to translate the document or to convert it to any electronic form in full or in parts without antecedent written approval of Fastwel Co. Ltd. or one of its officially authorized agents.

Fastwel and Fastwel logo are trademarks owned by Fastwel Co. Ltd., Moscow, Russian Federation. Ethernet is a registered trademark of Xerox Corporation. IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers Inc. Intel is a trademark of Intel Corporation. Geode is trademark of AMD. Microsoft is a trademark of the Microsoft corporation. In addition, this document may include names, company logos and trademarks, which are registered trademarks and, therefore, are property of their respective owners.

Fastwel welcomes suggestions, remarks and proposals regarding the form and the content of this Manual.

# **Notation Conventions**

#### Warning, ESD Sensitive Device!

This symbol draws your attention to the information related to electro static sensitivity of your product and its components. To keep product safety and operability it is necessary to handle it with care and follow the ESD safety directions.

#### Warning!

This sign marks warnings about hot surfaces. The surface of the heatsink and some components can get very hot during operation. Take due care when handling, avoid touching hot surfaces!

#### **Caution: Electric Shock!**

This symbol warns about danger of electrical shock (> 60 V) when touching products or parts of them. Failure to observe the indicated precautions and directions may expose your life to danger and may lead to damage to your product.

#### Warning!

Information marked by this symbol is essential for human and equipment safety. Read this information attentively, be watchful.

#### Note...

This symbol and title marks important information to be read attentively for your own benefit.

# **General Safety Precautions**

This product was developed for fault-free operation. Its design provides conformance to all related safety requirements. However, the life of this product can be seriously shortened by improper handling and incorrect operation. That is why it is necessary to follow general safety and operational instructions below.

## Warning!

All operations on this device must be carried out by sufficiently skilled personnel only.

# Warning!

When handling this product, special care must be taken not to hit the heatsink (if installed) against another rigid object. Also, be careful not to drop the product, since this may cause damage to the heatsink, CPU or other sensitive components as well.

Please, keep in mind that any physical damage to this product is not covered under warranty.

#### Note:

This product is guaranteed to operate within the published temperature ranges and relevant conditions. However, prolonged operation near the maximum temperature is not recommended by Fastwel or by electronic chip manufacturers due to thermal stress related failure mechanisms. These mechanisms are common to all silicon devices, they can reduce the MTBF of the product by increasing the failure probability. Prolonged operation at the lower limits of the temperature ranges has no limitations.

## Caution, Electric Shock!

Before installing this product into a system and before installing other devices on it, always ensure that your mains power is switched off.

Always disconnect external power supply cables during all handling and maintenance operations with this module to avoid serious danger of electrical shock.

# **Unpacking, Inspection and Handling**

Please read the manual carefully before unpacking the module or mounting the device into your system. Keep in mind the following:

## **ESD Sensitive Device!**

Electronic modules and their components are sensitive to static electricity. Even a non-perceptible by human being static discharge can be sufficient to destroy or degrade a component's operation! Therefore, all handling operations and inspections of this product must be performed with due care, in order to keep product integrity and operability:

- Preferably, unpack or pack this product only at EOS/ESD safe workplaces. Otherwise, it is important to be electrically discharged before touching the product. This can be done by touching a metal part of your system case with your hand or tool. It is particularly important to observe anti-static precautions when setting jumpers or replacing components.

- If the product contains batteries for RTC or memory back-up, ensure that the module is not placed on conductive surfaces, including anti-static mats or sponges. This can cause shortcircuit and result in damage to the battery and other components.

- Store this product in its protective packaging while it is not used for operational purposes.

# Unpacking

The product is carefully packed in an antistatic bag and in a carton box to protect it against possible damage and harmful influence during shipping. Unpack the product indoors only at a temperature not less than +15°C and relative humidity not more than 70%. Please note, that if the product was exposed to the temperatures below 0°C for a long time, it is necessary to keep it at normal conditions for at least 24 hours before unpacking. Do not keep the product close to a heat source.

Following ESD precautions, carefully take the product out of the shipping carton box. Proper handling of the product is critical to ensure correct operation and long-term reliability. When unpacking the product, and whenever handling it thereafter, be sure to hold the module preferably by the front panel, card edges or ejector handles. Avoid touching the components and connectors.

Retain all original packaging at least until the warranty period is over. You may need it for shipments or for storage of the product.

## **Initial Inspection**

Although the product is carefully packaged, it is still possible that shipping damages may occur. Careful inspection of the shipping carton can reveal evidence of damage or rough handling. Should you notice that the package is damaged, please notify the shipping service and the manufacturer as soon as possible. Retain the damaged packing material for inspection.

After unpacking the product, you should inspect it for visible damage that could have occurred during shipping or unpacking. If damage is observed (usually in the form of bent component leads or loose socketed components), contact Fastwel's official distributor from which you have purchased the product for additional instructions. Depending on the severity of the damage, the product may even need to be returned to the factory for repair. DO NOT apply power to the product if it has visible damage. Doing so may cause further, possibly irreparable damage, as well as result in a fire or electric shock hazard.

If the product contains socketed components, they should be inspected to make sure they are seated fully in their sockets.

# Handling

In performing all necessary installation and application operations, please follow only the instructions supplied by the present manual.

In order to keep Fastwel's warranty, you must not change or modify this product in any way, other than specifically approved by Fastwel or described in this manual.

Technical characteristics of the systems in which this product is installed, such as operating temperature ranges and power supply parameters, should conform to the requirements stated by this document.

Retain all the original packaging, you will need it to pack the product for shipping in warranty cases or for safe storage. Please, pack the product for transportation in the way it was packed by the supplier.

When handling the product, please, remember that the module, its components and connectors require delicate care. Always keep in mind the ESD sensitivity of the product.

# **Three Year Warranty**

Fastwel Co. Ltd. (Fastwel), warrants that its standard hardware products will be free from defects in materials and workmanship under normal use and service for the currently established warranty period. Fastwel's only responsibility under this warranty is, at its option, to replace or repair any defective component part of such products free of charge.

Fastwel neither assumes nor authorizes any other liability in connection with the sale, installation or use of its products. Fastwel shall have no liability for direct or consequential damages of any kind arising out of sale, delay in delivery, installation, or use of its products.

If a product should fail through Fastwel's fault during the warranty period, it will be repaired free of charge. For out of warranty repairs, the customer will be invoiced for repair charges at current standard labor and materials rates.

Warranty period for Fastwel products is 36 months since the date of purchase.

## The warranty set forth above does not extend to and shall not apply to:

- 1. Products, including software, which have been repaired or altered by other than Fastwel personnel, unless Buyer has properly altered or repaired the products in accordance with procedures previously approved in writing by Fastwel.

- 2. Products, which have been subject to power supply reversal, misuse, neglect, accident, or improper installation.

#### Returning a product for repair

- 1. Apply to Fastwel company or to any of the Fastwel's official representatives for the Product Return Authorization.

- 2. Attach a failure inspection report with a product to be returned in the form, accepted by customer, with a description of the failure circumstances and symptoms.

- 3. Carefully package the product in the antistatic bag, in which the product had been supplied. Failure to package in antistatic material will VOID all warranties. Then package the product in a safe container for shipping.

- 4. The customer pays for shipping the product to Fastwel or to an official Fastwel representative or dealer.

# 1 Introduction

This document presents general information on CPB906 CPU module, the details of its proper and safe installation, configuration and operation.

# 1.1 Module Introduction

CPB906 is the computer-on-module (COM) designed for use as a computing core in application specific embedded systems. CPB906 module is based on 32-bit x86 compatible highly-integrated Vortex86DX processor operating at 600 MHz with low power consumption and heat dissipation.

Small size (65x40 mm) of the CPB906 module together with low power consumption, high performance and functional expandability provide decisions flexibility in modern real-time control systems, industrial control systems, data aquisition and processing systems. It is equipped with wide range of interfaces, such as ISA, PCI, IDE/2xSDIO, 2xUSB2.0, Ethernet 10/100 Mbit, I2C, 2xRS232 (TTL), and GPIO.

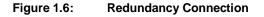

All basic interface signals are routed to carrier board through high-density 220-contact connector (3-6318490-6, COM-Express Connector Socket 220-pin Type I, TYCO). Signals necessary for building a redundancy system are routed to separate 10-contact connector (JST BM10B-SRSS-TB, SMT Vertical Top Entry 10-pin Plug 1.00 mm, SH-Series).

# 1.2 Main Specifications

- CPU: Integrated in DM&P Vortex86DX SoC

- 32-bit x86 x86 compatible core

- 16-bit memory bus

- Math coprocessor

- 32 KB L1, 256 KB L2 cache

- 6-stage pipeline

- System Memory

- 256 MB DDR2 SDRAM

- Soldered onboard

- DDR333

- Flash-disk

- 1 GB NAND Flash (SLC)

- Soldered onboard

- Connected to Secondary Master IDE channel

- Can be used as bootable device

- IDE port

- One Primary channel

- Connection of up to two external devices

- UltraDMA 100 support

- Flash BIOS

- 256 KB reserved. One copy in SPI-Flash embedded in processor, another – external Flash on the carrier board – ISA bus

- In-system modification

- Ethernet port:

- 10/100 Mb/s

- Operation mode LED indication

- USB ports (host):

- USB 1.1, USB 2.0 support

- Connection of up to two devices

- Serial ports:

- COM1: RS-232 (5-wires, TTL-levels)

- COM2: RS-232 (5-wires, TTL-levels)

- Each port additionally supports automatic data flow control signal

- Exchange rate: up to 115200 b/s

- 8-bit ISA expansion bus, 8/16 MHz

- 32-bit PCI expansion bus, 33 MHz

- LPC expansion bus

- PS/2 keyboard and mouse port

- I2C port

- Redundancy support

- Digital input/output port:

- 6 CMOS/TTL lines (5 V level compatible)

- 2 lines of embedded in the processor address decoder GPCS0#, GPCS1#;

I/O or Memory address space

- Input voltage: log. '0' max 0.8 V, log. '1' min 2.5 V

- Output voltage: log. '0' max 0.4 V @ 5 mA, log. '1' min 2.4 V @ 2 mA

- FPGA: XILINX XCS20-3TQ144I

- Two hardware watchdog timers:

- Embedded in the processor

- Programmable: 30.5 μs ... 512 s

- 64 Kbit FRAM for user data storage

- Real time clock: power off consumption current 2 μA (normal conditions)

- Onboard lithium battery: 3 V (CR2032; 180...200 mAh capacity)

- Hardware reset/interrupt port

- External Power Fail signal source port

- Interrupt/reset generation on the power supply voltage drop below 4.7 V

- PC-buzzer port

- Operatiing systems support:

- Microsoft<sup>™</sup> MS-DOS® 6.22

- Fastwel<sup>™</sup> FDOS 6.22

- Microsoft<sup>™</sup> Windows CE 5

- Linux 2.6

- QNX 6.4x

- Console ports

- COM1/COM2 and/or VGA/LCD (via an external video adapter) and/or keyboard

- Power supply voltage and consumption current:

- Not more than 5 V (± 10%) @ 450 mA (without external devices)

- Max. consumption current (including internal and external devices): 3 A (limited by onboard fuse)

- Additional power supply voltage generated by module for use by external devices on the carrier board:

- +3.3 V (± 5%) @ 400 mA

- Max. current: 500 mA

- Current is limited by self-resettable fuse

- Operating temperature range:

- Industrial: -40°..+85°C:(CPB906-01-I)

- Commercial: 0°...+70°C (CPB906-01-C)

- Relative humidity: up to 80%, non-condensing

- Storage conditions: 1 under GOST 15150-69

- Multiple shock resistance: 50 g

- Vibration resistance: 5 g

- MTBF: not less than 320000 hours The value is calculated according to: Telcordia Issue 1 model, Method I Case 3, for continuous operation at a surface location, at normal environmental conditions and at ambient temperature 30°C.

- Dimensions: 65.2×40.2×10.5 mm

- Weight: not more than 50 g

# 1.3 Functional Diagram

Functional diagram of the CPB906 module is shown in the figure below.

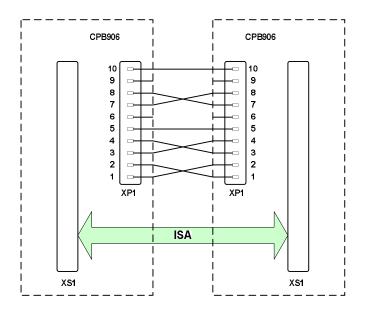

# 1.4 Appearance and Layout

The appearance may vary for different versions of the module.

The layout may slightly differ for various versions of the module.

Connectors of module are described in corresponding sections of this document. Switches X1...X5 are described in <u>Jumper Settings</u> section of this document.

# 1.5 CPB906 Versions

At the present time the CPB906 module is manufactured in four versions differing in operating temperature range and protective coating.

| Version             | Operating Temperature | Protective Coating |

|---------------------|-----------------------|--------------------|

| CPB906-01-I         | -40°C to +85°C        | -                  |

| CPB906-01-C         | 0°C to +70°C          | -                  |

| CPB906-01-I \COATED | -40°C to +85°C        | +                  |

| CPB906-01-C \COATED | 0°C to +70°C          | +                  |

Table 1.1:CPB906 Versions

# 1.6 Delivery Checklist

The standard delivery checklist of CPB906 processor module includes:

- 1. CPB906 processor module

- 2. CD-ROM with documentation and service software

- 3. Package

#### Note:

Keep the antistatic bag and the original package at least until the warranty period is over. It can be used for future storage or warranty shipments.

# 1.7 Additional Accessories

Additional accessories are not supplied with the CPU module, are ordered separately.

| Table 1.2: C | PB906 Additional Accessories |

|--------------|------------------------------|

|--------------|------------------------------|

| Name      | Description                                                                                                                                                                                                                                                                                                              |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| KIB880-01 | Carrier board for CPB906 processor module                                                                                                                                                                                                                                                                                |  |

| DVK906-01 | <ul> <li>Development kit including:</li> <li>CPB906 processor module</li> <li>KIB880 carrier board</li> <li>VIM301 video processor module</li> <li>Set of cables and adaptors</li> <li>CD with software and documentation including list of components and electric schematic diagram of KIB880 carrier board</li> </ul> |  |

| DVK906-02 | Development kit including in addition to DVK906-01 kit:<br>Windows CE 5.0 pre-installed on onboard flash-disk                                                                                                                                                                                                            |  |

| DVK906-03 | Development kit including in addition to DVK906-01 kit:<br>Linux 2.6 pre-installed on onboard flash-disk                                                                                                                                                                                                                 |  |

# **1.8 Functional Description**

## 1.8.1 Vortex86DX SoC

DM&P Vortex86DX includes the following main functional units:

- 32-bit x86 compatible core operating at 600 MHz;

- 32 KB L1, 256 KB L2 cache;

- Math coprocessor;

- 16-bit DDR2 SDRAM memory bus;

- IDE/SDIO controller;

- RS-232 serial ports;

- Universal parallel port;

- Four USB 2.0 ports;

- PS/2 keyboard/mouse port;

- PCI, ISA, LPC, and SPI bus controllers;

- I2C interface;

- Built-in Ethernet 10/100 controller;

- RTC;

- CMOS memory for configuration storage;

- Integrated flash-memory for BIOS storage;

- Integrated redundancy system;

- Two programmable watchdog timers.

# 1.8.2 XS1 Main High-Dencity Connector

All basic interfaces are routed to high-density 220-contact XS1 connector (TYCO 3-6318490-6, COM-Express Connector Socket, 220-pin, Type I).

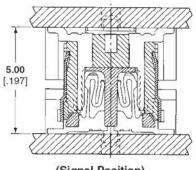

Figure 1.4: XS1 Main High-Dencity Connector

It is recommended to use as a counterpart on carrier board TYCO 3-1827253-6 (5 mm between CPB906 and carrier board) or TYCO 3-6318491-6 (8 mm distance).

#### Figure 1.5: Connection of CPB906 COM-Express Connector and the Carrier Board Counterpart

5mm Height

(Signal Position)

8mm Height

(Signal Position)

| Pin# | Signal      | In/Out       |

|------|-------------|--------------|

| A1   | GND (Fixed) | -            |

| A2   | ISA_GPCS1#  | Output       |

| A3   | ISA_GPCS0#  | Output       |

| A4   | ISA_SD6     | Input/Output |

| A5   | ISA_SA5     | Output       |

| A6   | ISA_SA1     | Output       |

| A7   | ISA_SD2     | Input/Output |

| A8   | ISA_SD4     | Input/Output |

| A9   | ISA_SA2     | Output       |

| A10  | ISA_SA3     | Output       |

| A11  | GND (Fixed) | -            |

| Pin# | Signal      | In/Out       |

|------|-------------|--------------|

| B1   | GND (Fixed) | -            |

| B2   | ISA_IOCHK#  | Input        |

| B3   | ISA_SD3     | Input/Output |

| B4   | ISA_IOR#    | Output       |

| B5   | ISA_IRQ9    | Input        |

| B6   | ISA_DACK2#  | Output       |

| B7   | ISA_MEMW#   | Output       |

| B8   | ISA_MEMR#   | Output       |

| B9   | ISA_SMEMR#  | Output       |

| B10  | ISA_SMEMW#  | Output       |

| B11  | GND (Fixed) | -            |

| Pin# | Signal            | In/Out                |

|------|-------------------|-----------------------|

| A12  | ISA_BCLK          | Output                |

| A13  | ISA_SA4           | Output                |

| A14  | ISA_SA19          | Output                |

| A15  | ISA_SA17          | Output                |

| A16  | ISA_SD0           | Input/Output          |

| A17  | ISA_SA10          | Output                |

| A18  | ISA_SD7           | Input/Output          |

| A19  | ISA_SA8           | Output                |

| A20  | ISA_SA9           | Output                |

| A21  | GND (Fixed)       | _                     |

| A22  | ISA_SA18          | Output                |

| A23  | ISA_SD5           | Input/Output          |

| A24  | ISA_SA0           | Output                |

| A25  | ISA_SA6           | Output                |

| A26  | ISA_SA14          | Output                |

| A27  | ISA_RST_DRV       | Output                |

| A28  | ISA_SA15          | Output                |

| A29  | ISA_DRQ3          | Input                 |

| A30  | ISA_ROMCS#        | Output                |

| A31  | GND (Fixed)       | -                     |

| A32  | GPIO_P0_5         | Input/Output          |

| A33  | GPIO_P0_3         | Input/Output          |

| A34  | GPIO_P0_0         | Input/Output          |

| A35  | GPIO_P0_1         | Input/Output          |

| A36  | GPIO_P0_4         | Input/Output          |

| A37  | GPIO_P0_2         | Input/Output          |

| A38  | IDE_D7            | Input/Output          |

| 730  | SD0_WP            | Input                 |

| A39  | IDE_D6<br>SD0_CD  | Input/Output<br>Input |

| A40  | IDE_D8<br>SD1_D2  | Input/Output          |

| A41  | GND (Fixed)       | -                     |

| A42  | IDE_D14           | Input/Output          |

|      | SD1_CD            | Input                 |

| A43  | IDE_CS1#          | Output                |

| A44  | IDE_D15<br>SD1_WP | Input/Output<br>Input |

| A45  | IDE_D4<br>SD0_D0  | Input/Output          |

| A46  | IDE_PDIAG#        | Input                 |

| Pin# | Signal       | In/Out         |  |  |

|------|--------------|----------------|--|--|

| B12  | ISA_OSC14M   | Out, 14.318MHz |  |  |

| B13  | ISA_AEN      | Output         |  |  |

| B14  | ISA_IRQ5     | Input          |  |  |

| B15  | ISA_IRQ7     | Input          |  |  |

| B16  | ISA_DACK3#   | Output         |  |  |

| B17  | ISA_SA7      | Output         |  |  |

| B18  | ISA_DACK1#   | Output         |  |  |

| B19  | ISA_IRQ6     | Input          |  |  |

| B20  | ISA_IRQ4     | Input          |  |  |

| B21  | GND (Fixed)  | -              |  |  |

| B22  | ISA_IOCHRDY# | Input          |  |  |

| B23  | ISA_IOW#     | Output         |  |  |

| B24  | ISA_0WS#     | Input          |  |  |

| B25  | ISA_REFRESH  | Output         |  |  |

| B26  | ISA_TC       | Output         |  |  |

| B27  | ISA_IRQ3     | Input          |  |  |

| B28  | ISA_DRQ2     | Input          |  |  |

| B29  | ISA_BALE     | Output         |  |  |

| B30  | ISA_DRQ1     | Input          |  |  |

| B31  | GND (Fixed)  | -              |  |  |

| B32  | ISA_SA13     | Output         |  |  |

| B33  | ISA_SD1      | Input/Output   |  |  |

| B34  | ISA_SA11     | Output         |  |  |

| B35  | ISA_SA12     | Output         |  |  |

| B36  | ISA_SA16     | Output         |  |  |

| B37  | IDE_D11      | Input/Output   |  |  |

| 207  | SD1_CLK      | Output         |  |  |

| B38  | IDE_IOR#     | Output         |  |  |

| B39  | IDE_DACK#    | Output         |  |  |

| B40  | IDE_IOW#     | Output         |  |  |

| B41  | GND (Fixed)  | -              |  |  |

| B42  | IDE_DRQ      | Input          |  |  |

| B43  | IDE_IORDY    | Input          |  |  |

| B44  | IDE_INT      | Input          |  |  |

| B45  | IDE_A2       | Output         |  |  |

| B46  | IDE_D3       | Input/Output   |  |  |

| Pin# | Signal           | In/Out       |

|------|------------------|--------------|

|      |                  |              |

| A47  | IDE_D0<br>SD0_D2 | Input/Output |

| A48  | IDE_A0           | Output       |

| A49  | IDE_CS0#         | Output       |

| A50  | SPK_DRV          | Input/Output |

| A51  | GND (Fixed)      | -            |

| A52  | LAN_TX-          | Output       |

| A53  | LAN_TX+          | Output       |

| A54  | GND              |              |

| A55  | LAN_RX+          | Input        |

| A56  | LAN_RX-          | Input        |

| A57  | GND              | -            |

| A58  | USB0_D+          | Input/Output |

| A59  | USB0_D-          | Input/Output |

| A60  | GND (Fixed)      | _            |

| A61  | COM1_RTS#        | Output       |

| A62  | COM2_RTS#        | Output       |

| A63  | COM2_TXD         | Output       |

| A64  | COM1_TXD         | Output       |

| A65  | COM2_RXD         | Input        |

| A66  | COM1_RXD         | Input        |

| A67  | COM2_TXEN        | Output       |

| A68  | COM1_CTS#        | Input        |

| A69  | COM2_CTS#        | Input        |

| A70  | GND (Fixed)      | -            |

| A71  | COM1_TXEN        | Output       |

| A72  | RMT_PFO#         | Input        |

| A73  | RMT_RESET#       | Input        |

| A74  | PCI_AD2          | Input/Output |

| A75  | PCI_AD3          | Input/Output |

| A76  | PCI_AD4          | Input/Output |

| A77  | PCI_AD0          | Input/Output |

| A78  | PCI_INTA#        | Input        |

| A79  | PCI_AD12         | Input/Output |

| A80  | GND (Fixed)      | _            |

| Pin# | Signal             | In/Out         |

|------|--------------------|----------------|

|      | SD0_CLK            | Output         |

| B47  | IDE_D1<br>SD0_D3   | Input/Output   |

| B48  | IDE_D9<br>SD1_D3   | Input/Output   |

| B49  | IDE_D5<br>SD0_D1   | Input/Output   |

| B50  | IDE_RST#           | Output         |

| B51  | GND (Fixed)        | _              |

| B52  | IDE_D2<br>SD0_CMD  | Input/Output   |

| B53  | IDE_D10<br>SD1_CMD | Input/Output   |

| B54  | IDE_D12<br>SD1_D0  | Input/Output   |

| B55  | IDE_A1             | Output         |

| B56  | IDE_D13<br>SD1_D1  | Input/Output   |

| B57  | GND                | _              |

| B58  | USB1_D+            | Input/Output   |

| B59  | USB1_D-            | Input/Output   |

| B60  | GND (Fixed)        | _              |

| B61  | LAN_LED_ACTIVE#    | Input/Output   |

| B62  | LAN_LED_DUPLEX#    | Input/Output   |

| B63  | CLOCK_24M          | Output, 24 MHz |

| B64  | LPC_AD3            | Input/Output   |

| B65  | LPC_SERIRQ         | Input/Output   |

| B66  | LPC_AD2            | Input/Output   |

| B67  | LPC_DRQ#           | Input          |

| B68  | LPC_AD0            | Input/Output   |

| B69  | LPC_AD1            | Input/Output   |

| B70  | GND (Fixed)        | -              |

| B71  | LPC_FRAME#         | Output         |

| B72  | MS_DAT             | Input/Output   |

| B73  | KB_DAT             | Input/Output   |

| B74  | KB_CLK             | Input/Output   |

| B75  | MS_CLK             | Input/Output   |

| B76  | I2C_SDA            | Input/Output   |

| B77  | I2C_SCL            | Input/Output   |

| B78  | PCI_AD1            | Input/Output   |

| B79  | PCI_FRAME#         | Input/Output   |

| B80  | GND (Fixed)        | _              |

| Pin# | Signal      | In/Out       |

|------|-------------|--------------|

| A81  | PCI_AD8     | Input/Output |

| A82  | PCI_AD7     | Input/Output |

| A83  | PCI_CBE1#   | Input/Output |

| A84  | PCI_AD5     | Input/Output |

| A85  | PCI_AD9     | Input/Output |

| A86  | PCI_AD10    | Input/Output |

| A87  | PCI_AD14    | Input/Output |

| A88  | PCI_AD13    | Input/Output |

| A89  | PCI_STOP#   | Input/Output |

| A90  | GND (Fixed) | -            |

| A91  | PCI_RESET#  | Output       |

| A92  | PCI_IRDY#   | Input/Output |

| A93  | PCI_TRDY#   | Input/Output |

| A94  | PCI_CBE3#   | Input/Output |

| A95  | PCI_AD26    | Input/Output |

| A96  | PCI_AD25    | Input/Output |

| A97  | PCI_GNT0#   | Output       |

| A98  | PCI_AD24    | Input/Output |

| A99  | PCI_PREQ0#  | Input/Output |

| A100 | GND (Fixed) | -            |

| A101 | PCI_AD30    | Input/Output |

| A102 | PCI_PREQ1#  | Input/Output |

| A103 | PCI_PREQ2#  | Input/Output |

| A104 | PCI_AD28    | Input/Output |

| A105 | PCI_AD29    | Input/Output |

| A106 | PCI_AD27    | Input/Output |

| A107 | VBAT        | Input/Output |

| A108 | +5V_POWER   | Input        |

| A109 | +5V_POWER   | Input        |

| A110 | GND (Fixed) | _            |

| Pin# | Signal      | In/Out       |