# Edsivel 23 H

CPC501

6U Compacted

6U Compacted

Mintel Pentium

Intel Board

CPU Board

User Manual

.

~

а

\_

q

.

\_

Φ

>

\_

-

n a

0

--

+

Φ

\_

⊏

-

S

Ø

≥

Ф

б

α

\_

S

.\_

\_

**—**

# **CPC501**

6U CompactPCI

Intel Pentium M Based

Processor Module

# **User Manual**

Rev. 0.03a E June 2006 Product Title: CPC501

Document name: CPC501 User Manual

Manual version: 0.03a E

Copyright © 2004, 2005, 2006 Fastwel Co. Ltd. All rights reserved.

#### **Revision Record**

| Rev. Index | Short Description                                                                                                                  | Product Index                | Date          |

|------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------|

| 0.01       | Initial version                                                                                                                    | CPC501                       | June 2004     |

| 0.02c      | Appendix A "Rear I/O module" added Chapter 5 changed Information on versions of the CPC501 and RIO581 added Minor corrections made | CPC50101<br>CPC50102         | June 2005     |

| 0.02e      | Changes in Gigabit/Fast Ethernet functionality added Information on RIO585 added                                                   | CPC501##<br>RIO581<br>RIO585 | November 2005 |

| 0.03       | Total text reassertion                                                                                                             | Same                         | February 2006 |

| 0.03a      | Watchdog timer section reworked, multiple text corrections                                                                         | Same                         | June 2006     |

#### **Contact Information**

#### Fastwel Co. Ltd.

Address: 108 Profsoyuznaya st., Moscow 117437, Russian Federation

Tel.: +7 (095) 234-0639

Fax: +7 (095) 232-1654

E-mail: info@fastwel.com

For more details, please visit our Web-site:

http://www.fastwel.com/

# **Table of Contents**

|   | Table  | e of Conte                            | nts            |                                                                                   | 0-1  |

|---|--------|---------------------------------------|----------------|-----------------------------------------------------------------------------------|------|

|   | List o | of Tables                             |                |                                                                                   | 0-4  |

|   | List o | of Figures                            |                |                                                                                   | 0-5  |

|   | Nota   | tion Conve                            | entions        |                                                                                   | 0-6  |

|   | Gene   | eral Safety                           | Precautions    | S                                                                                 | 0-7  |

|   | Unpa   | acking, Ins                           | pection and    | Handling                                                                          | 0-8  |

|   | Thre   | e Year Wa                             | arranty        |                                                                                   | 0-10 |

| 1 | Intro  | duction                               |                |                                                                                   | 1-1  |

|   | 1.1    | Overvie                               | :W             |                                                                                   | 1-1  |

|   | 1.2    | CPC50                                 | 1 Versions     |                                                                                   | 1-3  |

|   | 1.3    | CPC50                                 | 1 Diagrams     |                                                                                   | 1-4  |

|   |        | 1.3.1                                 | Block Dia      | gram                                                                              | 1-5  |

|   |        | 1.3.2                                 | Module A       | ppearance                                                                         | 1-6  |

|   |        | 1.3.3                                 | Compone        | ents and Connectors Layout                                                        | 1-7  |

|   |        | 1.3.4                                 | Front Pan      | nel                                                                               | 1-8  |

|   | 1.4    | Technic                               | al Character   | istics                                                                            | 1-9  |

|   |        | 1.4.1                                 | Processo       | r, Memory and Chipset                                                             | 1-9  |

|   |        | 1.4.2                                 | Interfaces     | S                                                                                 | 1-10 |

|   |        | 1.4.3                                 | Control ar     | nd Monitoring                                                                     | 1-12 |

|   |        | 1.4.4                                 | General        |                                                                                   | 1-13 |

|   |        | 1.4.5                                 | Software.      |                                                                                   | 1-13 |

|   | 1.5    | Informa                               | tion for Appli | cation Developers                                                                 | 1-14 |

|   | 1.6    | Delivery                              | / Checklist    |                                                                                   | 1-14 |

|   | 1.7    | System                                | Expansion      |                                                                                   | 1-15 |

|   |        | 1.7.1                                 | PMC Mod        | dules                                                                             | 1-15 |

|   |        | 1.7.2                                 | Rear I/O I     | Modules: RIO581 and RIO585                                                        | 1-15 |

| 2 | Deta   | ailed Des                             | cription       |                                                                                   | 2-1  |

|   | 2.1    | Process                               | sor, Memory    | and Chipset                                                                       | 2-1  |

|   |        | 2.1.1                                 |                | r                                                                                 |      |

|   |        | 2.1.2                                 |                | 1emory                                                                            |      |

|   |        | 2.1.3                                 | Chipset        | ·                                                                                 | 2-1  |

|   | 2.2    | Internal                              |                |                                                                                   |      |

|   |        | 2.2.1                                 | Flash Mei      | mory                                                                              | 2-3  |

|   |        |                                       | 2.2.1.1        | Flash Disk                                                                        | 2-3  |

|   |        |                                       | 2.2.1.2        | Compact Flash                                                                     | 2-3  |

|   |        | 2.2.2                                 | Hot-Swap       | Controller                                                                        | 2-3  |

|   |        | 2.2.3                                 | Timers         |                                                                                   | 2-3  |

|   |        |                                       | 2.2.3.1        | Watchdog Timer Operation Details                                                  | 2-4  |

|   |        | 2.2.4                                 | Local SM       | Bus Devices                                                                       | 2-6  |

|   |        |                                       | 2.2.4.1        | Temperatures Monitoring                                                           | 2-6  |

|   |        |                                       | 2.2.4.2        | Serial EEPROM                                                                     | 2-6  |

|   |        | 2.2.5                                 | Reset          |                                                                                   | 2-6  |

|   |        | 2.2.6                                 | Battery        |                                                                                   | 2-6  |

|   | 2.3    | Interfac                              | es             |                                                                                   | 2-7  |

|   |        | 2.3.1                                 | •              | /Mouse Interface                                                                  |      |

|   |        | 2.3.2 Serial Interfaces COM1 and COM2 |                |                                                                                   |      |

|   |        | 2.3.3 Serial Interfaces COM3 and COM4 |                |                                                                                   |      |

|   |        | 2.3.4                                 |                | faces                                                                             | 2-8  |

|   |        |                                       | 2.3.4.1        | USB Connectors J3 and J4 (front panel sockets) and J8 (onboard connector) Pinouts | 2.0  |

|   |        |                                       |                | F IIIUUI3                                                                         | ∠-9  |

|   |      | 2.3.5     | Graphics Controller                                                   | 2-10 |

|---|------|-----------|-----------------------------------------------------------------------|------|

|   |      |           | 2.3.5.1 DVM Technology                                                | 2-10 |

|   |      |           | 2.3.5.2 Supported Resolutions                                         | 2-10 |

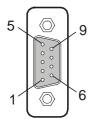

|   |      |           | 2.3.5.3 CRT Interface and Connector J7                                | 2-11 |

|   |      | 2.3.6     | Parallel Port Interface                                               | 2-11 |

|   |      | 2.3.7     | Gigabit Ethernet                                                      | 2-12 |

|   |      | 2.3.8     | Fast Ethernet                                                         | 2-14 |

|   |      | 2.3.9     | CompactFlash Socket                                                   | 2-16 |

|   |      | 2.3.10    | EIDE Interfaces                                                       | 2-18 |

|   |      | 2.3.11    | Floppy Drive Interface                                                | 2-19 |

|   |      | 2.3.12    | PMC Interface                                                         | 2-20 |

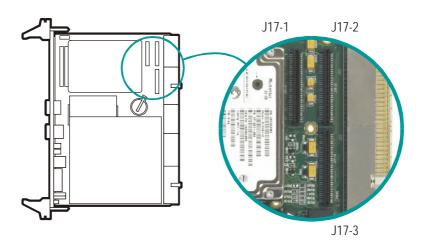

|   |      |           | 2.3.12.1 PMC Connectors J17-1 and J17-2 Pinouts                       | 2-21 |

|   |      | 2.3.13    | GP LEDs                                                               | 2-22 |

|   |      |           | 2.3.13.1 GP1 (CPC501) and GP (RIO581, RIO585) LEDs Control            | 2-22 |

|   |      |           | 2.3.13.2 GP2 LED Control                                              | 2-24 |

|   |      | 2.3.14    | CompactPCI Interface                                                  | 2-24 |

|   |      |           | 2.3.14.1 System Master Configuration                                  | 2-24 |

|   |      |           | 2.3.14.2 Peripheral Master Configuration (Passive Mode)               | 2-24 |

|   |      |           | 2.3.14.3 Packet Switching Backplane (PICMG 2.16)                      | 2-24 |

|   |      |           | 2.3.14.4 Hotswap Support                                              | 2-25 |

|   |      |           | 2.3.14.5 Power Ramping                                                | 2-25 |

|   |      |           | 2.3.14.6 Precharge                                                    | 2-25 |

|   |      |           | 2.3.14.7 Handle Switch                                                | 2-25 |

|   |      |           | 2.3.14.8 ENUM# Interrupt                                              | 2-25 |

|   |      |           | 2.3.14.9 Blue LED                                                     | 2-25 |

|   |      | 2.3.15    | CompactPCI Bus Connectors                                             | 2-26 |

|   |      |           | 2.3.15.1 CompactPCI Connector Color Coding                            |      |

|   |      |           | 2.3.15.2 CompactPCI Connectors J19 and J20 Pinouts                    |      |

|   |      |           | 2.3.15.3 CompactPCI Rear I/O Connectors J21-J23 (J3 – J5) and Pinouts |      |

|   |      |           | 2.3.15.4 Rear I/O Interfaces                                          |      |

| 3 | Inct | allation  |                                                                       |      |

| 3 |      |           |                                                                       |      |

|   | 3.1  | •         | Regulations                                                           |      |

|   | 3.2  |           | stallation                                                            |      |

|   | 3.3  |           | Removal                                                               |      |

|   | 3.4  | -         | O                                                                     |      |

|   |      | 3.4.1     | System Master Hotswap                                                 |      |

|   | 0 =  | 3.4.2     | Peripheral Hotswap                                                    |      |

|   | 3.5  | •         | ral Devices Installation                                              |      |

|   |      | 3.5.1     | USB Devices Installation                                              |      |

|   |      | 3.5.2     | CompactFlash Cards Installation                                       |      |

|   |      | 3.5.3     | Hard Disk Installation                                                |      |

|   |      | 3.5.4     | Battery Replacement                                                   |      |

|   |      | 3.5.5     | Rear I/O Modules Installation                                         | 3-6  |

| 4 | Con  | figuratio | n                                                                     | 4-1  |

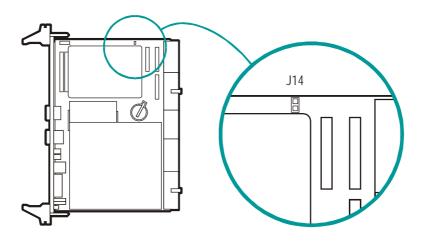

|   | 4.1  | J14 Jum   | per Description                                                       | 4-1  |

|   | 4.2  | Interrupt | ts Handling                                                           | 4-2  |

|   |      | 4.2.1     | On-board PCI Interrupts                                               |      |

|   | 4.3  | Memory    | Maps                                                                  |      |

|   |      | 4.3.1     | First Megabyte Memory Map                                             |      |

|   |      | 4.3.2     | I/O Addresses                                                         |      |

|   |      |           |                                                                       |      |

| 5 F | hoe  | enix® Bl                                   | OS Setup     |                                          | 5-1  |

|-----|------|--------------------------------------------|--------------|------------------------------------------|------|

| 5   | 5.1  | Boot De                                    | tails        |                                          | 5-1  |

|     |      | 5.1.1                                      | Booting w    | rithout a Monitor, Keyboard or Mouse     | 5-1  |

|     |      | 5.1.2                                      | Booting fr   | om USB                                   | 5-1  |

| 6 1 | Γher | mal and                                    | Power Iss    | ues                                      | 6-1  |

| 6   | 6.1  | Temper                                     | ature Contro | l                                        | 6-1  |

|     |      | 6.1.1                                      | Passive R    | Regulation                               | 6-1  |

|     |      | 6.1.2                                      | Active Re    | gulation                                 | 6-2  |

| 6   | 6.2  | System                                     | Power        |                                          | 6-3  |

| A F | Rear | · I/O Mod                                  | lules        |                                          | A-1  |

| A   | ۹.1  | Introduc                                   | tion         |                                          | A-1  |

|     |      | A.1.1                                      | Specificat   | tions                                    | A-1  |

|     |      | A.1.2                                      | Rear I/O I   | Modules Versions                         | A-1  |

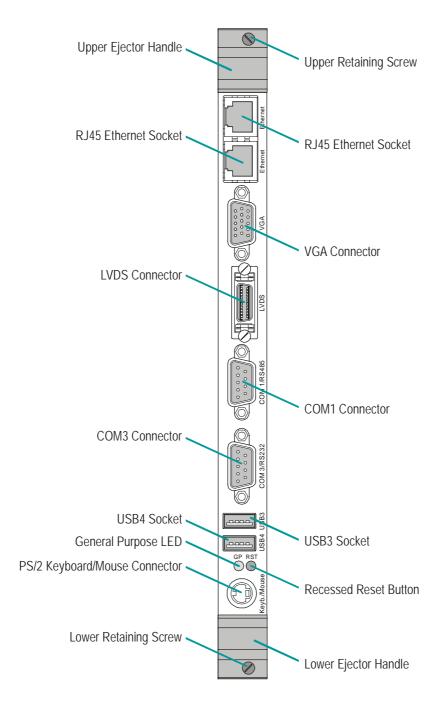

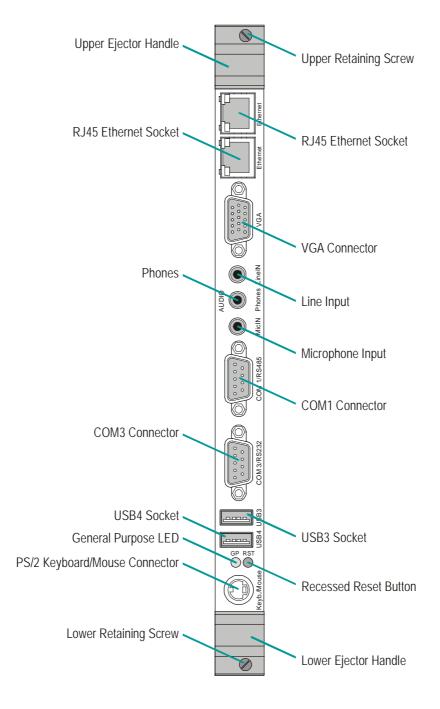

| A   | ۹.2  | Front Pa                                   | anel         |                                          | A-2  |

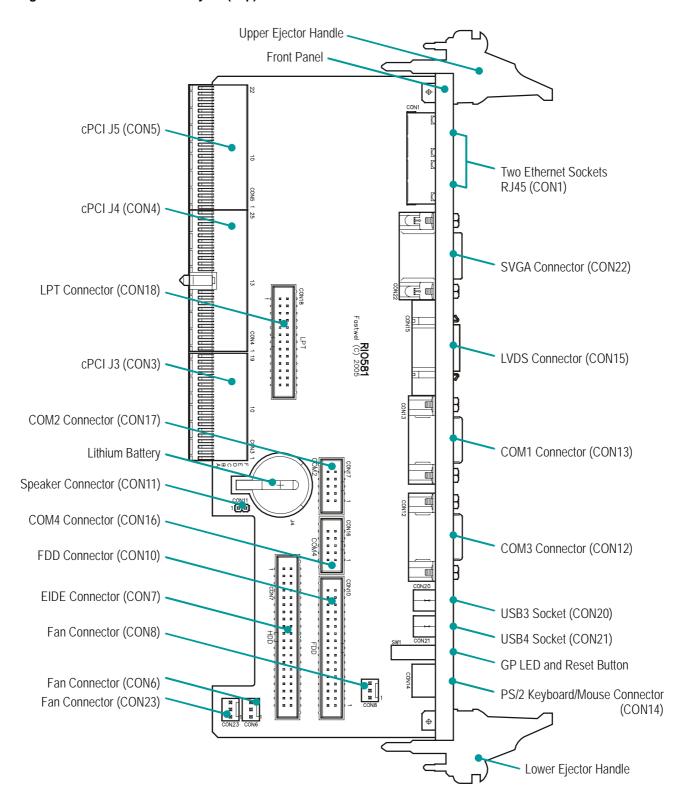

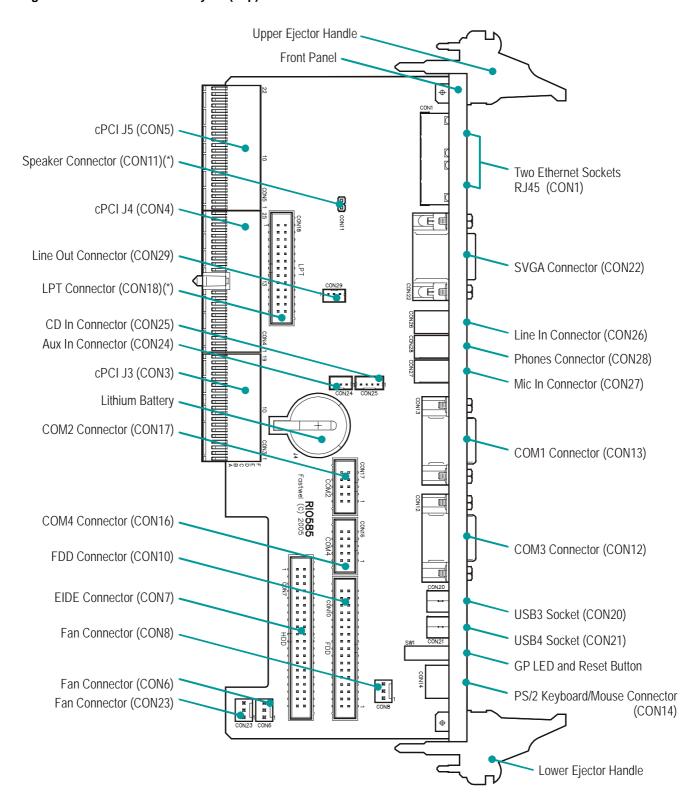

| A   | 4.3  | Rear I/C                                   | ) Modules La | ayout                                    | A-4  |

| A   | ۹.4  | RIO58x                                     | Delivery Che | ecklist                                  | A-6  |

| P   | ٩.5  | Rear I/C                                   | Modules In   | terfaces                                 | A-6  |

|     |      | A.5.1                                      | Overview     | of Modules Interfaces                    | A-6  |

|     |      |                                            | A.5.1.1      | Front Panel Interfaces                   | A-6  |

|     |      |                                            | A.5.1.2      | Onboard Interfaces and Connectors        | A-7  |

|     |      | A.5.2                                      | Detailed [   | Description of Modules Interfaces        | A-7  |

|     |      |                                            | A.5.2.1      | Keyboard/Mouse Interface                 | A-7  |

|     |      |                                            | A.5.2.2      | USB Interfaces                           | A-8  |

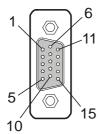

|     |      |                                            | A.5.2.3      | VGA-CRT Interface                        | A-9  |

|     |      |                                            | A.5.2.4      | LVDS Interface (RIO581 only)             | A-10 |

|     |      |                                            | A.5.2.5      | Serial Port Interfaces                   | A-11 |

|     |      |                                            | A.5.2.6      | Gigabit Ethernet Interfaces              |      |

|     |      |                                            | A.5.2.7      | EIDE Port                                |      |

|     |      |                                            | A.5.2.8      | Floppy Drive Interface                   |      |

|     |      |                                            | A.5.2.9      | LPT Interface                            |      |

|     |      |                                            | A.5.2.10     | Audio Interface and PC Speaker Connector |      |

|     |      |                                            | A.5.2.11     | Fan Control Interface                    |      |

|     |      |                                            | A.5.2.12     | CompactPCI Interface                     | A-18 |

| В 9 | Supp | plementa                                   | ary Informa  | ation                                    | B-1  |

| Е   | 3.1  | Related                                    | Standards a  | and Specifications                       | B-1  |

| : I | leaf | eful Abbreviations Acronyms and Short-cuts |              |                                          |      |

# **List of Tables**

| Table 2-1:  | SMBus Devices                                               | 2-6  |

|-------------|-------------------------------------------------------------|------|

| Table 2-2:  | Serial Port Connector J6 (COM1) Pinout                      | 2-7  |

| Table 2-3:  | USB Connectors J3 and J4 Pinouts                            | 2-9  |

| Table 2-4:  | USB Connector J8 Pinout                                     | 2-9  |

| Table 2-5:  | Supported Display Modes                                     | 2-10 |

| Table 2-6:  | CRT Connector J7 Pinout                                     | 2-11 |

| Table 2-7:  | Pinouts of Gigabit Ethernet Connectors J1A and J1B          | 2-13 |

| Table 2-8:  | RJ45 Fast Ethernet Connector J2 Pinout                      | 2-15 |

| Table 2-9:  | CompactFlash Socket J11 Pinout                              | 2-17 |

| Table 2-10: | Pinout of the AT EIDE J5 Connector                          |      |

| Table 2-11: | PMC Connectors J17-1 and J17-2 Pinouts                      | 2-21 |

| Table 2-12: | CompactPCI Coding Key Colors                                | 2-26 |

| Table 2-13: | CompactPCI Bus Connector J19 (J1) System Slot Pinout        | 2-27 |

| Table 2-14: | 64-bit CompactPCI Bus Connector J20 (J2) System Slot Pinout | 2-28 |

| Table 2-15: | Backplane J21 (J3) Pin Definition (PICMG 2.16 Pinout)       | 2-29 |

| Table 2-16: | Backplane J22 (J4) Pin Definitions                          | 2-30 |

| Table 2-17: | Backplane J23 (J5) Pin Definitions                          | 2-31 |

| Table 4-1:  | Interrupt Settings                                          | 4-2  |

| Table 4-2:  | PCI Interrupt Routing                                       | 4-2  |

| Table 4-3:  | First Megabyte Memory Map                                   | 4-3  |

| Table 4-4:  | I/O Address Map                                             | 4-3  |

| Table 6-1:  | DC Input Voltage Ranges and Limits                          | 6-3  |

| Table 6-2:  | CPC501 Components Power Consumption                         |      |

| Table A-1:  | Rear I/O Modules Versions                                   |      |

| Table A-2:  | Keyboard/Mouse Connector CON14 Pinout                       |      |

| Table A-3:  | USB Connectors CON20 and CON21 Pinouts                      |      |

| Table A-4:  | VGA Connector CON22 Pinout                                  | A-9  |

| Table A-5:  | LVDS Connector CON15 Pinout                                 |      |

| Table A-6:  | Functions of the Serial Port Interfaces                     |      |

| Table A-7:  | Serial Port Connectors CON17 (COM2) and CON16 (COM4) Pinout |      |

| Table A-8:  | Serial Port Connectors CON13 (COM1) and CON12 (COM3) Pinout |      |

| Table A-9:  | Pinouts of Gigabit Ethernet Connectors CON1A and CON1B      |      |

| Table A-10: | Pinout of AT Standard Secondary EIDE Connector              |      |

| Table A-11: | Floppy Drive Connector CON10 Pinout                         |      |

| Table A-12: | LPT Interface Connector CON18 Pinout                        | A-16 |

| Table A-13: | RIO585 Audio Interface Connectors                           | A-16 |

| Table A-14: | Audio Connectors CON24, CON25 and CON29 Pinouts             |      |

| Table A-15: | Fan Connectors CON6, CON8 and CON23 Pinouts                 |      |

| Table A-16: | Backplane J3 (CON3) Pin Definitions                         |      |

| Table A-17: | Backplane J4 (CON4) Pin Definitions                         |      |

| Table A-18: | Backplane J5 (CON5) Pin Definitions                         |      |

| Table B-1:  | Related Standards                                           | B-1  |

| Table B-2:  | Related Specifications                                      | B-1  |

## **List of Figures**

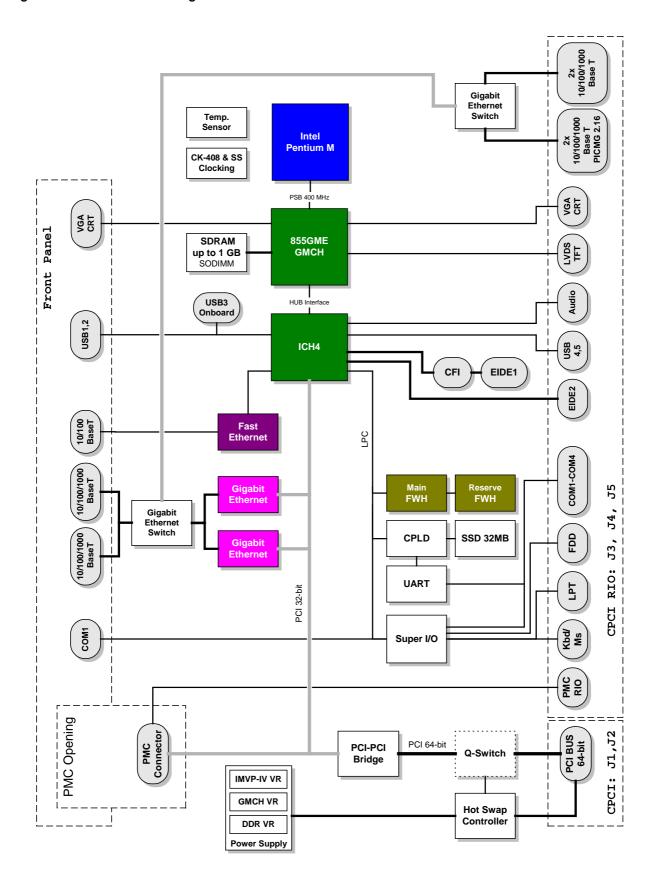

| Figure 1-1:  | CPC501 Block Diagram                                                          | 1-5  |

|--------------|-------------------------------------------------------------------------------|------|

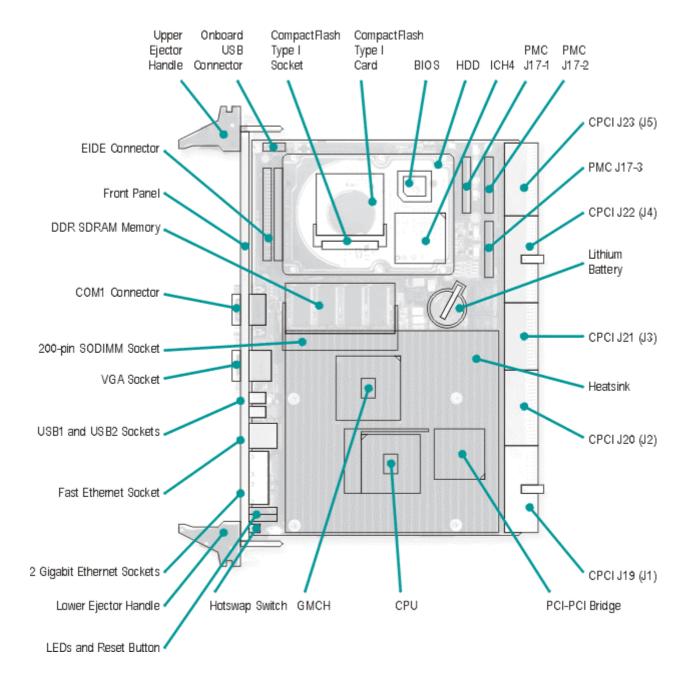

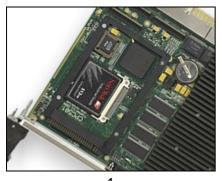

| Figure 1-2:  | CPC501 Module Appearance: Top, Front, Bottom Views                            | 1-6  |

| Figure 1-3:  | CPC501 Module Layout (Top View)                                               | 1-7  |

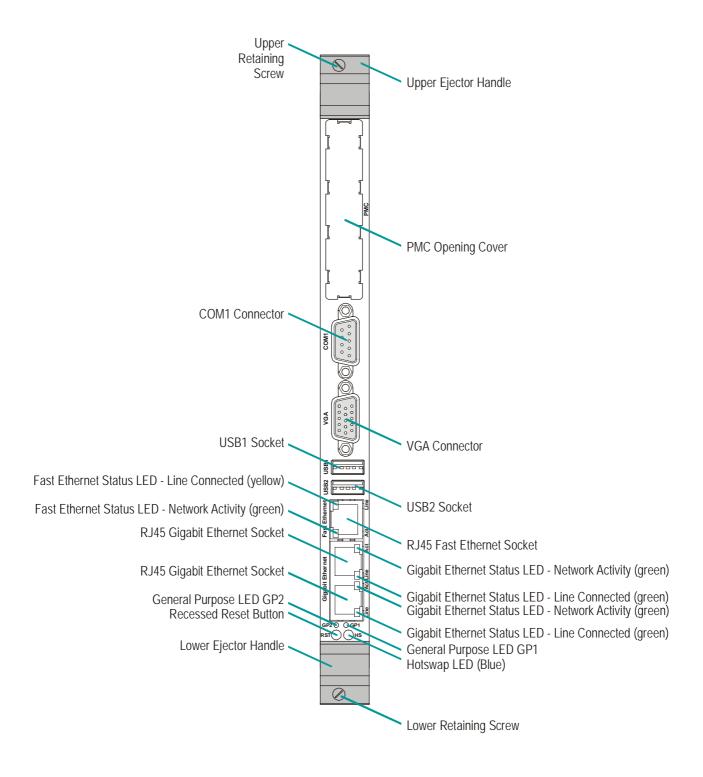

| Figure 1-4:  | CPC501 Front Panel (4HP)                                                      | 1-8  |

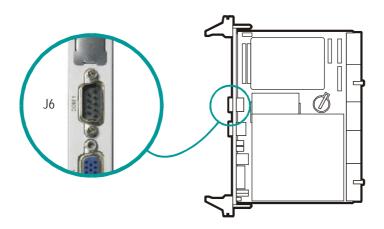

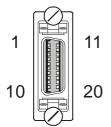

| Figure 2-1:  | PC-Compatible D-Sub Connector J6 (COM1)                                       | 2-7  |

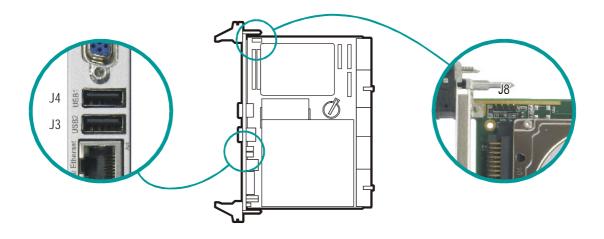

| Figure 2-2:  | USB Connectors J3, J4 and J8                                                  | 2-8  |

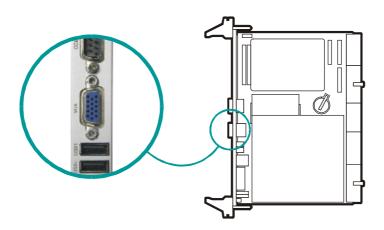

| Figure 2-3:  | CRT Connector J7                                                              | 2-11 |

| Figure 2-4:  | Gigabit Ethernet Connectors J1A and J1B                                       | 2-12 |

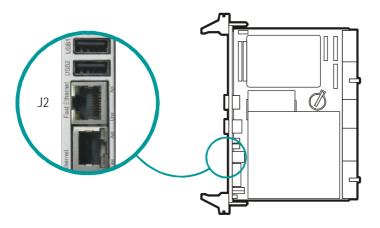

| Figure 2-5:  | Fast Ethernet Connector J2                                                    |      |

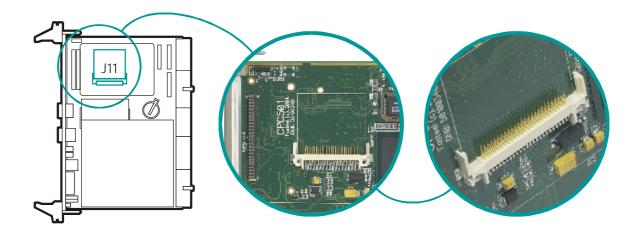

| Figure 2-6:  | CompactFlash Socket Connector J11                                             | 2-16 |

| Figure 2-7:  | EIDE Interface Connector J5 (HDD and HDD adapter not shown)                   | 2-18 |

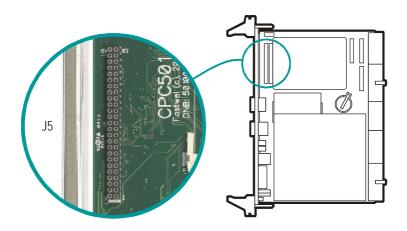

| Figure 2-8:  | PMC Connectors J17-1, J17-2 and J17-3                                         | 2-20 |

| Figure 2-9:  | CompactPCI Connectors J19 - J23 (J1 - J5 according to the cPCI specification) | 2-26 |

| Figure 4-1:  | Jumper J14 Location                                                           | 4-1  |

| Figure A-1:  | RIO581 Front Panel                                                            | A-2  |

| Figure A-2:  | RIO585 Front Panel                                                            | A-3  |

| Figure A-3:  | RIO581 Module Layout (Top)                                                    | A-4  |

| Figure A-4:  | RIO585 Module Layout (Top)                                                    | A-5  |

| Figure A-5:  | Keyboard/Mouse Connector CON14                                                | A-7  |

| Figure A-6:  | USB Connectors CON20 and CON21                                                | A-8  |

| Figure A-7:  | D-Sub VGA-CRT Connector CON22                                                 |      |

| Figure A-8:  | LVDS Connector CON15                                                          |      |

| Figure A-9:  | D-Sub Serial Connectors CON13 and CON12                                       |      |

| Figure A-10: | RIO58x Gigabit Ethernet Connectors                                            | A-13 |

|              |                                                                               |      |

All information in this document is provided for reference only, with no warranty of its suitability for any specific purpose. This information has been thoroughly checked and is believed to be entirely reliable and consistent with the product that it describes. However, Fastwel accepts no responsibility for inaccuracies, omissions or their consequences, as well as liability arising from the use or application of any product or example described in this document.

Fastwel Co. Ltd. reserves the right to change, modify, and improve this document or the products described in it, at Fastwel's discretion without further notice. Software described in this document is provided on an "as is" basis without warranty. Fastwel assumes no liability for consequential or incidental damages originated by the use of this software.

This document contains information, which is property of Fastwel Co. Ltd. It is not allowed to reproduce it or transmit by any means, to translate the document or to convert it to any electronic form in full or in parts without antecedent written approval of Fastwel Co. Ltd. or one of its officially authorized agents.

Fastwel and Fastwel logo are trademarks owned by Fastwel Co. Ltd., Moscow, Russian Federation. CompactPCI is a trademark of the PCI industrial Computers Manufacturers Group. Ethernet is a registered trademark of Xerox Corporation. IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers Inc. Intel is a trademark of Intel Corporation. Pentium M and Celeron M are trademarks of Intel Corporation. Microsoft is a trademark of the Microsoft corporation. In addition, this document may include names, company logos and trademarks, which are registered trademarks and, therefore, are property of their respective owners.

Fastwel welcomes suggestions, remarks and proposals regarding the form and the content of this Manual.

#### **Notation Conventions**

#### Warning, ESD Sensitive Device!

This symbol draws your attention to the information related to electro static sensitivity of your product and its components. To keep product safety and operability it is necessary to handle it with care and follow the ESD safety directions.

#### Warning!

This sign marks warnings about hot surfaces. The surface of the heatsink and some components can get very hot during operation. Take due care when handling, avoid touching hot surfaces!

#### Caution: Electric Shock!

This symbol warns about danger of electrical shock (> 60 V) when touching products or parts of them. Failure to observe the indicated precautions and directions may expose your life to danger and may lead to damage to your product.

#### Warning!

Information marked by this symbol is essential for human and equipment safety. Read this information attentively, be watchful.

#### Note...

This symbol and title marks important information to be read attentively for your own benefit.

# **General Safety Precautions**

This product was developed for fault-free operation. Its design provides conformance to all related safety requirements. However, the life of this product can be seriously shortened by improper handling and incorrect operation. That is why it is necessary to follow general safety and operational instructions below.

#### Warning!

All operations on this device must be carried out by sufficiently skilled personnel only.

#### Warning!

When handling this product, special care must be taken not to hit the heatsink (if installed) against another rigid object. Also, be careful not to drop the product, since this may cause damage to the heatsink, CPU or other sensitive components as well.

Please, keep in mind that any physical damage to this product is not covered under warranty.

#### Note:

This product is guaranteed to operate within the published temperature ranges and relevant conditions. However, prolonged operation near the maximum temperature is not recommended by Fastwel or by electronic chip manufacturers due to thermal stress related failure mechanisms. These mechanisms are common to all silicon devices, they can reduce the MTBF of the product by increasing the failure probability. Prolonged operation at the lower limits of the temperature ranges has no limitations.

#### Caution, Electric Shock!

Before installing this product into a system and before installing other devices on it, always ensure that your mains power is switched off.

Always disconnect external power supply cables during all handling and maintenance operations with this module to avoid serious danger of electrical shock.

# **Unpacking, Inspection and Handling**

Please read the manual carefully before unpacking the module or mounting the device into your system. Keep in mind the following:

#### **ESD Sensitive Device!**

Electronic modules and their components are sensitive to static electricity. Even a non-perceptible by human being static discharge can be sufficient to destroy or degrade a component's operation! Therefore, all handling operations and inspections of this product must be performed with due care, in order to keep product integrity and operability:

- Preferably, unpack or pack this product only at EOS/ESD safe workplaces. Otherwise, it is important to be electrically discharged before touching the product. This can be done by touching a metal part of your system case with your hand or tool. It is particularly important to observe anti-static precautions when setting jumpers or replacing components.

- If the product contains batteries for RTC or memory back-up, ensure that the module is not placed on conductive surfaces, including anti-static mats or sponges. This can cause short-circuit and result in damage to the battery and other components.

- Store this product in its protective packaging while it is not used for operational purposes.

#### Unpacking

The product is carefully packed in an antistatic bag and in a carton box to protect it against possible damage and harmful influence during shipping. Unpack the product indoors only at a temperature not less than +15°C and relative humidity not more than 70%. Please note, that if the product was exposed to the temperatures below 0°C for a long time, it is necessary to keep it at normal conditions for at least 24 hours before unpacking. Do not keep the product close to a heat source.

Following ESD precautions, carefully take the product out of the shipping carton box. Proper handling of the product is critical to ensure correct operation and long-term reliability. When unpacking the product, and whenever handling it thereafter, be sure to hold the module preferably by the front panel, card edges or ejector handles. Avoid touching the components and connectors.

Retain all original packaging at least until the warranty period is over. You may need it for shipments or for storage of the product.

#### **Initial Inspection**

Although the product is carefully packaged, it is still possible that shipping damages may occur. Careful inspection of the shipping carton can reveal evidence of damage or rough handling. Should you notice that the package is damaged, please notify the shipping service and the manufacturer as soon as possible. Retain the damaged packing material for inspection.

After unpacking the product, you should inspect it for visible damage that could have occurred during shipping or unpacking. If damage is observed (usually in the form of bent component leads or loose socketed components), contact Fastwel's official distributor from which you have purchased the product for additional instructions. Depending on the severity of the damage, the product may even need to be returned to the factory for repair. DO NOT apply power to the product if it has visible damage. Doing so may cause further, possibly irreparable damage, as well as result in a fire or electric shock hazard.

If the product contains socketed components, they should be inspected to make sure they are seated fully in their sockets.

#### Handling

In performing all necessary installation and application operations, please follow only the instructions supplied by the present manual.

In order to keep Fastwel's warranty, you must not change or modify this product in any way, other than specifically approved by Fastwel or described in this manual.

Technical characteristics of the systems in which this product is installed, such as operating temperature ranges and power supply parameters, should conform to the requirements stated by this document.

Retain all the original packaging, you will need it to pack the product for shipping in warranty cases or for safe storage. Please, pack the product for transportation in the way it was packed by the supplier.

When handling the product, please, remember that the module, its components and connectors require delicate care. Always keep in mind the ESD sensitivity of the product.

## **Three Year Warranty**

Fastwel Co. Ltd. (Fastwel), warrants that its standard hardware products will be free from defects in materials and workmanship under normal use and service for the currently established warranty period. Fastwel's only responsibility under this warranty is, at its option, to replace or repair any defective component part of such products free of charge.

Fastwel neither assumes nor authorizes any other liability in connection with the sale, installation or use of its products. Fastwel shall have no liability for direct or consequential damages of any kind arising out of sale, delay in delivery, installation, or use of its products.

If a product should fail through Fastwel's fault during the warranty period, it will be repaired free of charge. For out of warranty repairs, the customer will be invoiced for repair charges at current standard labor and materials rates.

Warranty period for Fastwel products is 36 months since the date of purchase.

#### The warranty set forth above does not extend to and shall not apply to:

- 1. Products, including software, which have been repaired or altered by other than Fastwel personnel, unless Buyer has properly altered or repaired the products in accordance with procedures previously approved in writing by Fastwel.

- 2. Products which have been subject to power supply reversal, misuse, neglect, accident, or improper installation.

#### Returning a product for repair

- 1. Apply to Fastwel company or to any of the Fastwel's official representatives for the Product Return Authorization.

- 2. Attach a failure inspection report with a product to be returned in the form, accepted by customer, with a description of the failure circumstances and symptoms.

- 3. Carefully package the product in the antistatic bag, in which the product had been supplied. Failure to package in antistatic material will VOID all warranties. Then package the product in a safe container for shipping.

- 4. The customer pays for shipping the product to Fastwel or to an official Fastwel representative or dealer.

Fastwel

Chapter 1

Introduction

.

~

а

\_

q

.

\_

Φ

>

\_

-

n a

0

--

+

Φ

\_

⊏

-

S

Ø

≥

Ф

б

α

\_

S

.\_

\_

**—**

# 1 Introduction

#### 1.1 Overview

The CPC501 is an advanced 64-bit / 33 MHz 6U CompactPCI system controller module. To get the details about the CompactPCI, a wide spread industrial standard, please refer to PCI and CompactPCI specifications. The Internet site of the PCI Industrial Computer Manufacturers Group (PICMG) provides information related to these standards (http://www.picmg.org/).

The CPC501 processor module is specially developed for use in highly integrated systems for performance-demanding industrial applications. This is one of the main reasons to employ Intel® Pentium® M processors family. The CPC501 basic configuration utilizes the processor in the  $\mu\text{FCPGA478M}$  package operating at the processor speed of up to 2 GHz and a Processor Side Bus (PSB) running at 400 MHz. The chipset of the CPC501 includes the Intel 82855GME GMCH and ICH4 I/O Controller Hub.

The module includes up to 1 GB of Double Data Rate (DDR) memory. It is installed in one 200-pin SODIMM socket and is operated at 333 MHz.

System features include two Gigabit Ethernet ports, one Fast Ethernet port (82559-style), and one PMC slot to support mezzanine PCI devices (option). The module also includes a built-in Intel 2D/3D Graphics accelerator with up to 64 MB memory shared with system for enhanced graphics performance with a VGA CRT-display interface and with TFT LVDS interface.

The CPC501 is equipped with the following PC interfaces including: five USB 2.0 ports, four COM ports, two EIDE ATA100 interfaces, one CompactFlash Type I socket, one Floppy port, one parallel port, and, besides, rear I/O CompactPCI bus connectors J3, J4, and J5.

The module supports one configurable 64-bit, 33 MHz, hotswap CompactPCI interface. In the system master slot the bridge is enabled, and if installed in a peripheral slot, the CPC501 is isolated from the CompactPCI-bus.

One of the most important features of the CPC501 is its support of the PICMG CompactPCI Packet Switching Backplane Specification 2.16. When installed in a backplane which supports packet switching, the CPC501 can communicate via both of its Gigabit Ethernet interfaces with other peripherals or a system master which also support packet switching.

CPC501 employs the thoroughly selected components for embedded industrial systems to ensure their long term availability.

The module is compatible with the Microsoft® DOS v.3.30 – 6.22, Microsoft® Windows® CE, 2000, Windows® XP, QNX v.4.20, 6.0, and Linux® operating systems.

#### Some of the CPC501's main features are:

- Intel® Pentium® M processor up to 2.0 GHz in µFCPGA package

- Up to 2 MB L2 on-die cache running at CPU speed

- 82855GME GMCH and 82801DB ICH4 chipset

- 400 MHz processor system bus

- Up to 1 GB of DDR SDRAM memory running at 333 MHz (PC2700) with ECC

- PCI local bus: 32-bit / 33 MHz

- CompactPCI-bus interface: 64-bit / 33 MHz

- Integrated 3D high performance VGA controller

- 64 MB memory shared with system

- CRT-display support with resolutions of up to 2048 x 1536 pixels at 16 bits and 75 Hz

- LVDS interface support via Rear I/O

- Four serial ports

- Five USB 2.0 ports

- PS/2 keyboard and mouse interface

- Floppy disk interface

- Parallel port

- Two Gigabit Ethernet interfaces

- 10Base-T, 100Base-TX, and 1000Base-T

- Independently software configurable for cPCI backplane packet switching (PICMG® 2.16, R1.0), for CPC501 front panel or for RIO58x front panel interfacing.

- One integrated Fast Ethernet interface (82559-style), 82562ET, 10Base-T, 100Base-TX

- PMC interface (32-bit) with rear I/O support and opening on front panel. Standard PMC modules can be installed on CPC50102 version only.

- Two EIDE Ultra ATA/100 interfaces

- Onboard CompactFlash Type I socket

- Optional socket for 2.5" hard disk or flash-disk on board (CPC50101 only)

- Hardware Monitor (LM82)

- Watchdog timer

- Additional counters and timers integrated in the ICH4

- Real-time clock with battery backup

- Two 512 KB on-board FWHs

- 4HP, 6U CompactPCI form-factor

- Hotswap capability: as system controller or as peripheral device

- Supports PICMG® Packet Switching Backplane Specification v.2.16

- Rear I/O on J3, J4 and J5

- Passive heatsink solution

- Phoenix® BIOS

# 1.2 CPC501 Versions

At the present time, the module is manufactured in two basic versions:

| Version  | On-board 2.5" HDD or flash-disk capability | Standard PMC modules capability |

|----------|--------------------------------------------|---------------------------------|

| CPC50101 | +                                          | -                               |

| CPC50102 | -                                          | +                               |

Moreover, the CPC501 configuration is flexible. The customer can choose necessary configuration options using the following template:

1 - 2 - 3 - 4 - 5

1 Basic product name:

CPC501

2 Basic configurations:

01 On-board 2.5" HDD or flash-disk capability

02 Standard PMC modules capability

3 Processor:

P1.6 Pentium M 1.6 GHz, 400 MHz FSB P1.8 Pentium M 1.8 GHz, 400 MHz FSB

4 Operating temperature range:

I Industrial, -40°C to +85°C

C Commercial, 0°C to 70°C

5 Other options:

**SODIMM Memory Module**

\SODIMM512 512 MB DDR SDRAM SODIMM, Industrial Range \SODIMM512C 512 MB DDR SDRAM SODIMM, Commercial Range \SODIMM1024 1024 MB DDR SDRAM SODIMM, Industrial Range \SODIMM1024C 1024 MB DDR SDRAM SODIMM, Commercial Range

CompactFlash Module

\CF128 128 MB CompactFlash card, industrial \CF256 256 MB CompactFlash card, industrial \CF512 512 MB CompactFlash card, industrial \CF1024 1024 MB CompactFlash card, industrial

Installed 2.5" Disk Drive (for CPC50101 only)

\HDD20 2.5" Hard Disk Drive, 20 GB \FFD2048 2.5" Flash Disk, 2048 MB

Coating

\COATED Protective Coating

#### Examples:

#### CPC501 - 01 - P1.8 - I \SODIMM1024

6U CompactPCI Pentium M SBC, FFD 32 MB, VGA, 2x Gigabit Ethernet 2.5" HDD Site Pentium M 1.8 GHz, 400 MHz FSB Industrial operating temperature range, -40°C to +85°C 1024 MB DDR SDRAM SODIMM, industrial range

#### CPC501 - 01 - P1.6 - C \SODIMM512C \CF128 \HDD20 \COATED

6U CompactPCI Pentium M SBC, FFD 32 MB, VGA, 2x Gigabit Ethernet Pentium M 1.6 GHz, 400 MHz FSB Commercial operating temperature range, 0°C ... +70°C 512 MB DDR SDRAM SODIMM, commercial range 128 MB CompactFlash card HDD 2.5" 20 GB Protective coating

Other configuration options are available upon request.

# 1.3 CPC501 Diagrams

The diagrams in this section give visual information about the CPC501 module design, its appearance, connectors and components layout. The diagrams may not reflect insignificant differences between the CPC501 versions.

# 1.3.1 Block Diagram

Figure 1-1: CPC501 Block Diagram

# 1.3.2 Module Appearance

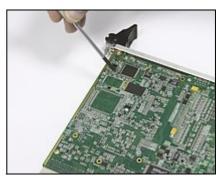

Figure 1-2: CPC501 Module Appearance: Top, Front Views

The appearance may slightly differ for various versions of the module.

This figure shows CPC50101 with a 2.5" HDD installed on-board.

# 1.3.3 Components and Connectors Layout

Figure 1-3: CPC501 Module Layout (Top View)

The layout may differ for various versions of the module:

CPC50101 – has J5 connector, does not have J17-3 PMC connector; CPC50102 – does not have J5 EIDE connector, has J17-1, J17-2 u J17-3

#### 1.3.4 Front Panel

Figure 1-4: CPC501 Front Panel (4HP)

The layout may slightly differ for various versions of the module.

#### 1.4 Technical Characteristics

#### 1.4.1 Processor, Memory and Chipset

#### **CPU**

#### Pentium® M Processor

- Up to 2.0 GHz

- Up to 2 MB L2 on-die cache

- 400 MHz PSB

- Supports SpeedStep® III for low power mode

- 478-pin μFCPGA package

#### Memory

#### Main memory:

- Up to 1 GB of DDR SDRAM memory in a 200-pin SODIMM socket, ECC support

- Memory frequency: 333 MHz (PC2700)

#### Flash memory:

- Two flash memory Firmware Hubs (part of the CPC501 chipset) used for BIOS storage

- One 256 byte EEPROM for storing CMOS data when operating without battery

- Up to 32 MB solid-state disk (NAND flash memory) with Fastwel file system

#### Chipset

#### Intel® 82855GME Graphics Memory Controller Hub (GMCH)

- Support for a single Pentium M family microprocessors

- 64-bit AGTL/AGTL+ based System Bus interface at 400 MHz

- 64-bit System Memory interface, optimized for DDR SDRAM memory at 333 MHz with additional 8-bits for ECC

- Integrated 2D/3D Graphics and H/W Motion Compensation Engines

- Integrated DAC, 350 MHz

#### Intel® 82801DB I/O Controller Hub (ICH4)

- PCI Rev. 2.2 compliant with support for 33 MHz/32-bit PCI bus

- Enhanced DMA controller, interrupt controller, and timer

- Integrated Ultra ATA100 IDE controller

- USB 2.0 host interface

- One integrated 82559-type LAN controller

- System Management Bus

- Power management logic support

- Low Pin Count (LPC) interface

- Firmware Hub (FWH) interface support

- Additional timers

#### 1.4.2 Interfaces

#### CompactPCI Bus Interface

Compliant with CompactPCI Specification PICMG® 2.0 R3.0

- System master operation

- 64-bit / 33 MHz master interface

- 3.3V / 5.0V compatible (default configuration is 5.0V)

- When the CPC501 is operated in a peripheral slot, the CPCI-bus is electrically isolated from the CPC501

#### **Serial Ports**

#### COM1 and COM2:

- COM1 RS-232, 9-pin D-sub connector on the CPC501 front panel

- COM2 TTL level signals, available at the Rear I/O only

- Dual UART, 16C550 compatible

#### COM3 and COM4:

- 16C550 compatible UARTs

- Rear I/O availability only

- TTL level signals

#### **USB** Interface

Five USB 2.0 ports supporting UHCI and EHCI:

- Two USB type A connectors on the front panel

- Two rear I/O interfaces

- One onboard port connector

#### **Parallel Port**

Multi-Mode™ parallel port, SPP/ECP/EPP compatible

- Standard Mode IBM PC/XT, PC/AT, and PS/2 compatible bidirectional parallel port

- Rear I/O interfacing only

#### **Gigabit Ethernet**

Two 10/100/1000 Mb/s Gigabit Ethernet interfaces based on the Intel 82541EI Ethernet PCI bus controller.

- Two RJ45 connectors on the front panel

- Support for two Gigabit Ethernet channels independently software configurable for cPCI backplane packet switching (PICMG® 2.16, R1.0), for CPC501 front panel or for RIO58x front panel interfacing.

- Automatic mode recognition

- Automatic cabling configuration recognition

- Cabling requirement: Category 5, UTP, four-pair cabling

#### **Fast Ethernet**

One 10Base-T/100Base-TX Fast Ethernet port integrated within the ICH4 controller (82559-type):

- One RJ45 connector on the CPC501 front panel

- Automatic mode recognition

- Cabling requirement: Category 5, UTP, two-pair cabling.

#### **VGA** interface

Built-in Intel 2D/3D high performance graphics accelerator

- Supports resolutions of up to 2048 x 1536, 16 bit at 75 Hz refresh rate

- Hardware motion compensation for software MPEG2 and MPEG4 decoding

- Video memory up to 64 MB shared with system

- 15-pin D-sub VGA CRT-display connectors available at CPC501 and at RIO58x front panels

#### **Keyboard and Mouse**

Super I/O support for a keyboard and a mouse:

- Rear I/O interfacing for both keyboard and mouse

- Standard PS/2 keyboard connector (6-pin), requires adaptor

(Y-cable) to connect regular mouse and a keyboard simultaneously

#### **Mass Storage**

#### EIDE Ultra ATA/100/66/33

- Two channels

- Up to four devices (hard disks or CD-ROMs)

- Optional 50-pin, 2.0 mm, female connector for mounting a 2.5" disk drive onboard (CPC50101 only)

#### CompactFlash:

CompactFlash type I on-board socket (true IDE mode), supports type I CompactFlash cards

#### Floppy Disk:

- Rear I/O interfacing only

- Supports 5.25 or 3.5 inch floppy drives

- 1.44 or 2.88 MB, 3.5 inch floppy disks

#### **PMC**

CMC / PMC P1386 / Draft 2.4a compliant mezzanine interface:

- J17-1 (Jn1), J17-2 (Jn2), and J17-3 (Jn4) PCI mezzanine connectors for standard PMC modules (CPC50102 only)

- 32-bit / 33 MHz master interface

- 3.3 V compatible

- Rear I/O supported through CompactPCI connector J23 (J5)

#### Rear I/O

To optimize cabling rear I/O interface is available via the J21 (J3), J22 (J4), and J23 (J5) connectors in combination with the rear I/O modules RIO58x.

- J21 (J3): floppy, COM3, keyboard, mouse, USB4, secondary EIDE port and PICMG 2.16 support.

- J23 (J5): VGA-CRT, two Ethernet channels without LEDs, USB5, COM1, COM2, COM4, control signals, PMC rear I/O connectivity

- J22 (J4): parallel port, AC-link, LVDS (RIO58101)

#### 1.4.3 Control and Monitoring

#### **Thermal Management**

Processor is protected from overheating by the following means:

- The processor frequency and core voltage are automatically reduced when processor die temperature reaches the limit specified in BIOS Setup

- Internal processor temperature control unit initiates CPU shut down when the processor die is overheated

- Processor die temperature monitor helps to keep the processor temperature within prescribed limits

- Custom designed heatsinks provide efficient heat energy dissipation

#### **Temperature Monitor**

LM82 hardware monitor is used for supervision of the on-die CPU temperature and the board surface temperature

#### **Hotswap Compatibility**

The CPC501 supports System Master hotswap and application dependent hotswap when used in a peripheral slot.

When used as a System Master the CPC501 supports individual clocks for each slot and ENUM signal handling in accordance with the PICMG 2.1 R2.0 Hotswap specification.

#### **LEDs**

#### System status:

- GP1 (red): Programmable

- GP2 (green): Programmable

- HS: blue: Hotswap control

#### Gigabit Ethernet status (1 and 2):

- Line (green): Line connected

- Act (green): Network activity

#### Fast Ethernet status:

- Line (yellow): Line connected

- Act (green): Network activity

#### **Switches**

#### Reset switch (RST):

- Initiates cold restart of CPC501

- The button is recessed to prevent accidental activation (can be activated using long thin object)

#### Hotswap switch:

- When activated initiates safe power off

- Integrated as part of the lower ejector handle

#### 1.4.4 General

#### Mechanical

6U, 4HP, CompactPCI compliant form factor

Dimensions:  $233.35 \text{ mm} \times 160 \times 20.32 \text{ mm}$

Module Weight: 835 g with 2.5" hard disk and without mezzanine boards,

725 g without HDD

#### **Power Supply**

2 A @ +3.3 V; 6 A @ +5 V; 0.1 A @ +12 V (without external devices)

See Chapter 6 for details on supply voltages and power supply requirements

#### **Temperature Ranges**

Operational: CPC501-01-xxx-I, CPC501-02-xxx-I -40°C ... +85°C

Storage: -55°C ... +85°C

#### Humidity

5% to 95% RH, non-condensing

#### **Battery**

3.0 V lithium battery for RTC in a battery holder. Use PANASONIC BR2032 or compatible

#### 1.4.5 Software

#### **Software BIOS**

Flash memory based enhanced Phoenix® BIOS has the following features:

- BIOS boot support for USB keyboards

- Software enable/disable function for the Rear I/O, Ethernet, and COM ports configuration

- Plug&Play capability

#### **Operating Systems**

Supported operating systems:

- Microsoft® Windows® 2000, XP, CE

- Microsoft® DOS v. 3.x 6.x

- Linux®

- ONX®

# 1.5 Information for Application Developers

Please, consider the following information when developing applications using the CPC501.

#### **Hotswap Compatibility**

When operated as a system master, the CPC501 supports individual clocks for each slot and ENUM signal handling is in compliance with the CompactPCI Hot Swap Specification PICMG 2.1 R2.0. When operated in a peripheral slot the CPC501 supports basic Hotswap.

#### System Slot / System Master Functionality

The CPC501 is designed to for use as a system master board whereby it can support up to 7 peripheral boards with 64-bit and 33 MHz. It may, however, be operated in a peripheral slot. In this case it does not support the CompactPCI-bus interface.

#### **Peripheral Slot Functionality**

When installed in a peripheral slot, the CPC501 is electrically isolated for the CompactPCI-bus. It receives power from the backplane and supports rear I/O and, if the system supports it, packet switching (in this case up to two channels of Gigabit Ethernet).

## 1.6 Delivery Checklist

The CPC501 supplied set includes:

- 1. CPC501 processor module

- 2. 2.5" HDD mounting kit (for installation of a 2.5" HDD, for CPC50101 only):

- HDD mounting adapter with connectors

- Four screws (M3)

- 3. CD-ROM with documentation and service software

- Antistatic bag

- 5. Consumer package

#### Note:

Keep the antistatic bag and the original package at least until the warranty period is over. It can be used for future storage or warranty shipments.

# 1.7 System Expansion

#### 1.7.1 PMC Modules

The CPC501 has one PMC interface. This 32-bit, 33 MHz interface supports a wide range of available standard PMC modules and provides a convenient way to adapt the CPC501 for various applications. PMC modules can be installed only on CPC50102, which has three PMC connectors and no J5 EIDE connector.

#### 1.7.2 Rear I/O Modules: RIO581 and RIO585

Rear I/O modules expand the I/O capability of the CPC501. They are installed from the back of the system crate in line with the processor module. For detailed information concerning RIO581 and RIO585 modules, please, refer to <a href="https://www.fastwel.com/">http://www.fastwel.com/</a>

.

¥

⊆

α

\_

Р

+

-

Φ

\_

>

\_

\_

\_

-

Ф

+

.\_

S

α

≥

Φ

a O

..

\_

\_

Fashvel

Chapter 2

**Detailed Description**

.

~

а

\_

q

.

\_

Φ

>

\_

-

n a

0

--

+

Φ

\_

⊏

-

S

Ø

≥

Ф

б

α

\_

S

.\_

\_

**—**

# 2 Detailed Description

# 2.1 Processor, Memory and Chipset

#### 2.1.1 Processor

The CPC501 module is based on the Intel® Pentium® M processor in the  $\mu$ FCPGA478M package. It combines high performance and low power consumption. Its enhanced performance characteristics are provided by a newly designed processor core with an integrated 64 KB L1 and 2048 KB L2 cache.

The Intel® Pentium® M processor supports the Intel SpeedStep® enhanced technology to control power consumption and processor die temperature by switching the processor core voltage and frequency between several modes without resetting the system. This allows the system to maintain maximum performance rate at different temperature conditions.

Important performance features of the Intel Pentium M Processor also include Intel NetBurst™ Micro-Architecture, consisting of a 400 MHz processor system bus, Hyper Pipelined Technology, new Execution Trace Cache, Rapid Execution Engine, and 144 new Streaming SIMD instruction extensions.

# 2.1.2 System Memory

The CPC501 has one on-board 200-pin DDR SODIMM socket. The module supports a maximum of 1 GB. There is no need to make any additional settings, since the installed memory is automatically detected by the system. The SODIMM memory modules to be used with this module must conform to PC2700, and PC SPD (Serial Presence Detect) DDR SDRAM memory specifications.

The memory module is not included in the basic configuration.

#### 2.1.3 Chipset

The Intel® 855GME chipset consists of the following devices:

- 82855GME Graphics and Memory Controller Hub (GMCH) with Accelerated Hub Architecture (AHA) bus

- 82801DB I/O Controller Hub 4 (ICH4) with AHA bus

- Two 82802AB Firmware Hubs (FWH)

The GMCH provides the interfaces for the Pentium® M microprocessor, the memory bus, the AGP 4x bus in the case of an external graphics controller installed. It includes a high performance 2D/3D built-in graphics accelerator. The ICH4 serves as a central controller for I/O peripherals, such as the PCI, EIDE, USB 2.0, LAN and Audio ports. The Firmware Hubs (FWH) provide the non-volatile storage of BIOS.

#### **North Bridge**

The 855GME Graphics Memory Controller Hub (GMCH) provides interfaces with the central processor, with the DDR SDRAM system memory, and interface to high performance internal graphics or AGP interface for an external VGA controller. It also provides a hub link interface to the ICH4.

The 855GME is optimized for the Intel® Pentium® M family of microprocessors. The chipset supports a PSB frequency of 400 MHz with AGTL+ signaling. For single processor systems the single ended AGTL termination is supported. It supports 32-bit addressing for using up to 4 GB memory address space. The 855GME includes a system memory controller with a 64-bit interface with ECC. The chipset supports up to PC2700 DDR SDRAMs for use as system memory.

When running in internal graphics mode, high performance video capabilities of the 855GME are supported by a 2D/3D graphics accelerator and H/W Motion Compensation engines for software MPEG2 decoding. The internal graphics controller allows connection of a standard CRT display.

#### **South Bridge**

The ICH4 is a multifunctional I/O Controller Hub that provides the interface to the PCI Bus and such PC interfaces, as UltraDMA 100/66/33, USB 2.0 host interface, LPC interface, FWH Flash BIOS interface, LAN interface and an AC'97 digital audio. The ICH4 communicates with the host controller directly via a dedicated hub link interface.

I/O Controller Hub features are:

- PCI 2.2 interface with eight IRQ inputs

- UltraDMA 100 EIDE controller with Bus Master capability

- Three USB controllers, up to six USB 2.0 ports

- Hub interface for 855GME

- LPC interface

- Integrated 82559-type LAN controller

- AC'97 2.1 audio interface

- RTC controller

- Additional timers

# 2.2 Internal Peripherals

The following internal peripherals are available on the CPC501 module:

# 2.2.1 Flash Memory

There are four flash devices available - one is used for the BIOS storage, one is reserved (not used in current version), one is a NAND flash memory (SSD) device and one is a CompactFlash card in the socket.

#### 2.2.1.1 Flash Disk

The CPC501 has an on-board solid-state disk (up to 32 MB of NAND flash-memory) with Fastwel file system for storing user programs and data.

#### 2.2.1.2 Compact Flash

The CPC501 has a standard Compact Flash type I socket, which can accept CompactFlash memory card for use as a disk drive.

# 2.2.2 Hot-Swap Controller

The purpose of the hot-swap controller is to provide safe disconnection of power when the module is removed from the system and to ensure correct power-up when the module is installed into the system crate.

As a part of the hot-swap controller, a precision voltage monitoring circuit automatically shuts down CPC501 when it detects a drop in voltage below the acceptable operating limit of 4.725 V for the 5 V line and below 3.0 V for the 3.3 V line, or in the event of a power failure of the processor DC/DC converter.

# 2.2.3 Timers

The CPC501 is equipped with the following timers:

#### Real-Time Clock

The ICH4 contains a real-time clock compatible with MC146818A with 256 bytes of CMOS RAM. The RTC features include timekeeping with alarm function and 100-year calendar, as well as programmable periodic interrupt. A coin-cell battery powers the real-time clock and CMOS memory.

#### Counters/Timers

Three PC/AT 8254-style counters/timers are available on the CPC501.

# Watchdog Timer

The ICH4 includes an additional programmable timer (TCO timer), which prevents system hangups during the start-up process (for example, in case of mistakes in BIOS) and during normal operation. After the first time-out period is over, it generates the SMI# signal, which may start the software hang-up recovery subroutine. After the second timeout comes to an end, the "Reset" signal is issued to recover the system from the hardware hang-up state.

The timeout period is set in BIOS Setup program or by the user program.

# 2.2.3.1 Watchdog Timer Operation Details

The watchdog timer is switched on by setting the TCO\_TMR\_HLT bit of the TCO1\_CNT register to 0 and is stopped by setting this bit to 1.

The timer is initially loaded with the value from the TCO1\_TMR register and begins countdown. After the first timeout is over, the SECOND\_TO\_STS bit is set and if the TCO\_EN bit of the SMI\_EN register is set, SMI interrupt is issued. Along with it, the timer is again loaded with the value from the TCO1\_TMR register and begins countdown for the second time.To prevent system reset, the SMI handler, if it is enabled in BIOS Setup, clears the SECOND\_TO\_STS bit. After the second timeout period is over and the SECOND\_TO\_STS bit is still set, the PCI\_RESET signal is issued and the system is rebooted.

In case the TCO\_TMR\_HLT bit is cleared and either the SMI Handler is disabled or the TCO\_EN bit is cleared, then to prevent system reset the user program should either reload the watchdog timer by writing any value to the TCO\_RLD register within the first timeout period, or clear the SECOND\_TO\_STS bit by writing 1 to it before the second timeout period is over.

Please refer to Intel® 82801DB I/O Controller Hub 4 (ICH4) Datasheet for the complete description of registers. The description of TCO timer operation related registers is quoted below.

#### **TCO Timer Registers Description**

#### TCO1\_RLD - TCO Timer Reload and Current Value Register

I/O Address:1060hAttribute:R/WDefault Value:0000hSize:8 bitLockable:NoPower Well:Core

| Bit | Description                                                                                                                                                                       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Reading this register will return the current count of the TCO timer. Writing any value to this register will reload the timer to prevent the timeout. Bits 7:6 will always be 0. |

#### TCO1 TMR - TCO Timer Initial Value Register

I/O Address:1061hAttribute:R/WDefault Value:0004hSize:8 bitLockable:NoPower Well:Core

| Bit | Description                                                                                                                                                                                                                                                     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Reserved                                                                                                                                                                                                                                                        |

| 5:0 | Value that is loaded into the timer each time the TCO_RLD register is written. Values of 0h–3h will be ignored and should not be attempted. The timer is clocked at approximately 0.6 seconds, and this allows timeouts ranging from 2.4 seconds to 38 seconds. |

# TCO2\_STS - TCO2 Status Register

I/O Address: 1066h Attribute: R/WC Default Value: 0000h Size: 16 bit Power Well: Lockable: No Resume

| Bit  | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:2 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1    | SECOND_TO_STS - R/WC.  0 = This bit is cleared by writing a 1 to the bit position or by a RSMRST#.  1 = The ICH4 sets this bit to a 1 to indicate that the TCO timer timed out a second time (probably due to system lock). If this bit is set, then the ICH4 will reboot the system after the second timeout. The reboot is done by asserting PCIRST#.  NOTE: BIOS should always clear this bit before executing SMBus reads and writes. |

| 0    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# TCO1\_CNT - TCO1 Control Register

1068h I/O Address: Attribute: R/W, R/WC, R/W-Special

0000h Default Value: Size: 16 bit Lockable: Power Well: No Core

| Bit   | Description                                                                                                                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | Reserved                                                                                                                                                                                                                                                     |

| 11    | TCO Timer Halt (TCO_TMR_HLT) – R/W.  0 = The TCO Timer is enabled to count.  1 = The TCO Timer will halt. It will not count, and thus cannot reach a value that will cause an SMI# or set the SECOND_TO_STS bit.  When set, this bit will prevent rebooting. |

| 10:0  | Reserved                                                                                                                                                                                                                                                     |

# SMI\_EN - SMI Control and Enable Register

1030h Attribute: I/O Address: R/W, WO, R/W-Special

Default Value: 0000h Size: 32 bit

Lockable: Usage: **ACPI** or Legacy No

Power Well: Core

| Bit   | Description                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------|

| 31:14 | Reserved                                                                                               |

| 13    | TCO_EN – R/W.  0 = Disables TCO logic generating an SMI#.  1 = Enables the TCO logic to generate SMI#. |

| 12:0  | Reserved                                                                                               |

#### 2.2.4 Local SMBus Devices

The CPC501 incorporates a System Management Bus to access several system monitoring and control devices via a two-wire I<sup>2</sup>C<sup>™</sup> bus interface. The following table presents functions and addresses of onboard SMBus devices.

Table 2-1: SMBus Devices

| Nº | SMB Address | Device                          |  |  |  |

|----|-------------|---------------------------------|--|--|--|

| 1  | 0D2H        | CS950201 System clock generator |  |  |  |

| 2  | 0D4H        | FT Suspend Generator ICS91718   |  |  |  |

| 3  | 0A0H        | SPD EEPROM Module               |  |  |  |

| 4  | 9CH         | LM82 Temperature Sensor         |  |  |  |

| 5  | 0ACH, 0AEH  | 2×256 Bytes User EEPROM         |  |  |  |

# 2.2.4.1 Temperatures Monitoring

The integrated LM82 temperature sensor monitors the processor and board surface temperatures to make sure that the system is operating at a safe temperature. On request, LM82 can report the current processor and board temperatures to the software responsible for the module operation mode.

#### 2.2.4.2 Serial EEPROM

A serial EEPROM is implemented into the hot-swap controller (SMH4042). This nonvolatile memory is used for storage of CMOS data and some of the service parameters for emergency recovery.

#### 2.2.5 Reset

Reset sources include the front panel and Rear I/O push-button switches, and CompactPCI backplane reset input (PRST). The CPC501 responds to any of these sources' signal by initializing local peripherals.

# 2.2.6 Battery

The CPC501 utilizes a 3.0 V lithium battery for the RTC and CMOS memory backup. Use PANASONIC BR2032 or compatible.

# 2.3 Interfaces

# 2.3.1 Keyboard/Mouse Interface

The onboard keyboard controller is 8042 software compatible.

The keyboard and mouse port is routed to the CompactPCI rear I/O interface. There is no front I/O connector available at CPC501. To connect a keyboard and/or a mouse a 6-pin MiniDIN connector CON14 is available at the front panel of RIO581 and RIO585 Rear I/O modules. Keyboard and mouse simultaneous connection requires Y-cable.

#### 2.3.2 Serial Interfaces COM1 and COM2

Figure 2-1: PC-Compatible D-Sub Connector J6 (COM1)

One PC-compatible serial 9-pin D-sub connector (COM1) is available on the front panel as a RS-232 port. COM2 is available at the Rear I/O only. Both COM ports are fully compatible with the 16550 controller and include a complete set of handshaking and modem control signals, maskable interrupt generation and data transfer rate of up to 460.8 Kb/s.

Serial port COM1 can be switched to front panel or to the Rear I/O from inside the BIOS Setup program. The standard configuration is front I/O.

The two COM interfaces may be used at the Rear I/O as either RS-232, RS-422 or RS-485 ports via suitable adapter.

Table 2-2: Serial Port Connector J6 (COM1) Pinout

| Pin Number | Function | Pin Number | Function |

|------------|----------|------------|----------|

| 1          | DCD      | 6          | DSR      |

| 2          | RXD      | 7          | RTS      |

| 3          | TXD      | 8          | CTS      |

| 4          | DTR      | 9          | RIN      |

| 5          | GND      |            |          |

# 2.3.3 Serial Interfaces COM3 and COM4

Additionally, two PC-compatible serial ports with TTL signal level are available. These two COM ports, which are fully compatible with the 16550 controller, include a complete set of handshaking and modem control signals, and maskable interrupt generation. **The COM3 and COM4 ports are available on the CompactPCI Rear I/O interface only.**

#### 2.3.4 USB Interfaces

The CPC501 supports five USB 2.0 ports (two front I/O, one onboard interface and two on the Rear I/O module). All five ports support high-speed, full-speed, and low-speed operation. Hi-speed USB 2.0 supports data transfer rate of up to 480 Mb/s.

#### Note:

Some USB devices connected to the Rear I/O sockets may work in USB 1.1 mode only.

Only one USB device may be connected to each port. To connect more than five USB devices use an external hub.

The USB power supply is protected by a self-resettable 500 mA fuse.

Figure 2-2: USB Connectors J3, J4 and J8

The pinouts of the USB connectors appear on the following page.

# 2.3.4.1 USB Connectors J3 and J4 (front panel sockets) and J8 (onboard connector) Pinouts

The CPC501 has three USB interfaces (two more available via rear I/O) implemented on 4-pin connectors with the following pinouts:

Table 2-3: USB Connectors J3 and J4 Pinouts

| Pin Number Signal |      | Function          | In/Out |

|-------------------|------|-------------------|--------|

| 1                 | VCC  | VCC signal        | -      |

| 2                 | UV0- | Differential USB- | -      |

| 3                 | UV0+ | Differential USB+ | -      |

| 4                 | GND  | GND signal        | _      |

Table 2-4: USB Connector J8 Pinout

| Pin Number | Signal | Function          | In/Out |

|------------|--------|-------------------|--------|

| 1          | VCC    | VCC signal        | -      |

| 2          | UV0-   | Differential USB- | -      |

| 3          | UV0+   | Differential USB+ | _      |

| 4          | GND    | GND signal        | _      |

# 2.3.5 Graphics Controller

A highly integrated 2D/3D graphics accelerator is included in the 855GME chipset. The internal graphics controller provides interfaces to a standard analog monitor or/and to a digital TFT panel with LVDS interface. The LVDS socket is available at Fastwel's RIO581 front panel.

Main features of an integrated 2D/3D graphics controller are:

- Resolutions up to 1600×1200 at 100 Hz, 1920×1440 at 85 Hz and 2048×1536 at 75 Hz

- 3D Setup and Render Engine