# **CPC507**

SoC AMD FP5 APU Based 6U Compact PCI CPU Module

# **User Manual**

Rev. 002 August 2022

The product described in this manual is compliant with all related CE standards.

Product Title: CPC507 Document name: CPC507 User Manual Manual version: 002 Ref. docs:

Copyright © 2022 Fastwel Co. Ltd. All rights reserved.

#### **Revision Record**

| Rev. Index | Brief Description     | Product Index | Date          |

|------------|-----------------------|---------------|---------------|

| 001        | Initial version       | CPC507        | February 2021 |

| 002        | Compliance assessment | CPC507        | August 2022   |

|            |                       |               |               |

#### **Contact Information**

|          | Fastwel Co. Ltd                                                |         | Fastwel Corporation US                                      |

|----------|----------------------------------------------------------------|---------|-------------------------------------------------------------|

| Address: | 108 Profsoyuznaya St.,<br>Moscow 117437,<br>Russian Federation |         | 6108 Avenida Encinas,<br>Suite B, Carlsbad,<br>CA92011, USA |

| Tel.:    | +7 (495) 232-1681                                              | Tel.:   | +1 (858) 488-3663                                           |

| Fax:     | +7 (495) 232-1654                                              |         |                                                             |

| E-mail:  | info@fastwel.com                                               | E-mail: | info@fastwel.com                                            |

| Web:     | http://www.fastwel.com/                                        |         |                                                             |

### **Table of Contents**

| Та            | ble of Contents                                      | . 1 |

|---------------|------------------------------------------------------|-----|

| Lis           | t of Tables                                          | 2   |

| Lis           | t of Figures                                         | 3   |

| Co            | nventions                                            | .5  |

|               | neral rules of usage                                 |     |

|               | nufacturer's warranties                              |     |

|               | ansportation, Unpacking and Storage                  |     |

|               | RODUCTIOIN                                           |     |

|               | System overview                                      |     |

|               | General description of the module                    |     |

|               | Module versions                                      |     |

|               |                                                      |     |

|               | General Features of CPC507                           |     |

|               | Compatibility with the PICMG/VITA standards          |     |

|               | Device dimensions                                    |     |

|               | Delivery checklist                                   |     |

|               | Derational conditions                                |     |

|               | Product labeling                                     |     |

|               | Packaging information                                |     |

|               | SIGN ĂNĂ OPERATION                                   |     |

| 3.1 E         | Block diagram                                        | 17  |

|               | Specific performance features of functional nodes    |     |

|               | System expansion options                             |     |

| 3.3           | 3.1 PMC/XMC Modules                                  | 19  |

| 3.4 l         | Jsing the module in the CPCI system                  | 19  |

| 3.5 l         | Location of main components                          | 20  |

| 4. INT        | ENDED USE                                            | 21  |

| 4.1 ľ         | Module Interfaces                                    | 21  |

| 4             | 4.1.1 XMC interface                                  | 21  |

| 4             | 1.1.2 PMC interface                                  | 22  |

|               | 1.1.3 SATA interface                                 |     |

|               | 1.1.4 COM port                                       |     |

|               | 1.1.5 Connectors on the front panel of CPC507        |     |

|               | 1.1.6 LEDs on the front panel of CPC507              |     |

|               | .1.7 Using the module in CompactPCI system           |     |

|               | 1.1.8 Compact PCI connectors                         |     |

|               | Fimers                                               |     |

|               | 4.2.1 Watchdog Timer                                 |     |

|               | 4.2.2 Description of I/O registers of WDT controller |     |

| 4.3 \$        | SPI controller / LEDs / GPIO                         |     |

|               | 4.3.1 Description of SPI controller registers.       |     |

|               | 4.3.2 Programming SPI device.                        |     |

|               | 4.3.3 FRAM with sequential access                    |     |

|               | Devices on the local SMBus                           |     |

|               | TALLATION                                            |     |

| <b>5. INS</b> | Safety requirements                                  |     |

| 5.1<br>5.2    | CPC507 installation procedure                        |     |

| 5.2<br>5.3    | Board Removal Procedure                              |     |

| 5.3<br>5.4    | Installing peripherals to CPC507                     |     |

| 0.7           | 5.4.1 Connecting USB devices                         |     |

| 5.5           | Battery replacement.                                 |     |

| 5.6           | Installing CFast Drive                               |     |

|               | STEM SETUP                                           |     |

| 6.1 Resetting the BIOS Se | etup settings        |    |

|---------------------------|----------------------|----|

| 7. AMI APTIO BIOS SETU    | P                    | 47 |

| 7.1 Starting and Updating | BIOS Setup           | 47 |

|                           | S Setup              |    |

| 7.1.2 Navigation ke       | eys                  | 47 |

|                           |                      |    |

| 7.2 Advanced              |                      | 49 |

| 7.2.1 Fastwel Feat        | ures                 |    |

| 8. CPC507 TROUBLESHO      | OTING                | 50 |

| 9. POWER CONSUMPTION      | Ν                    | 51 |

| ANNEX A: TERMS. ACRONY    | MS AND ABBREVIATIONS |    |

|                           |                      |    |

|                           |                      |    |

### List of Tables

| Table 1-1: Versions of CPC507                                                              | 11 |

|--------------------------------------------------------------------------------------------|----|

| Table 2-1: Delivery checklist                                                              | 15 |

| Table 2-2: Operational ranges of external influencing factors                              | 15 |

| Table 3-1: System information                                                              | 19 |

| Table 4-1: Purpose of XMC1 XS7 (P15) and XMC2 XS8 (P15) connector pins on the CPC507 board | 21 |

| Table 4-2: PMC connector pin assignment                                                    | 23 |

| Table 4-3: Assignment of SATA XS6 connector pins                                           | 24 |

| Table 4-4: Assignment of XP2 connector pins                                                | 25 |

| Table 4-5: Assignment of USB connector pins on the front panel of CPC507                   | 26 |

| Table 4-6: Assignment of Gigabit Ethernet connector pins                                   | 26 |

| Table 4-7: Assignment of XS1 DisplayPort connector pins of the CPC507 module               | 27 |

| Table 4-8: State of the SYS LED of the CPC507 module                                       | 28 |

| Table 4-9: Color code designations of connectors                                           | 31 |

| Table 4-10: Assignment of pins of the CompactPCI XS20 (J1) system connector                | 31 |

| Table 4-11: Pin assignment of the XS18 (J2) system connector of 64-bit CompactPCI bus      | 32 |

| Table 4-12: Pin assignment of the XS21 (J3) connector of CPC507                            | 33 |

| Table 4-13: Assignment of the XS19 (J4) connector pins of the CPC507 module                | 34 |

| Table 4-14: Assignment of the XS17 (J5) connector pins of CPC507                           | 35 |

| Table 4-15: Timer Current Value Register [23:0]                                            | 37 |

| Table 4-16: Timer Initial Value Register [23:0]                                            | 37 |

| Table 4-17: Status Register                                                                | 38 |

| Table 4-18: Control Register                                                               | 38 |

| Table 4-19: Registers of the SPI controller                                                | 39 |

| Table 4-20: Device addresses on SMBus                                                      | 41 |

| Table 7-1: Assignment of navigation keys                                                   | 47 |

| Table 7-2: Setting the Fastwel Features                                                    | 49 |

| Table 8-1: Causes of module faults and their rectifications                                | 50 |

| Table 9-1: Supply voltage of +5 V,+3.3 V,+12 V,-12 V fed from the CPCI bus                 | 51 |

| Table A 1 – Terms, acronyms and abbreviations                                              | 52 |

### **List of Figures**

| Figure 2-1: Device dimensions                                                               | 14 |

|---------------------------------------------------------------------------------------------|----|

| Figure 3-1: Block diagram of the device                                                     | 17 |

| Figure 3-2: Location of the main components of CPC507                                       | 20 |

| Figure 4-1: XMC XS7 (P15) and XS8 (P15) connectors                                          | 21 |

| Figure 4-2: Connectors PMC XS10 (P3), XS11 (P1), XS12 (P3) and XS13 (P2)                    | 22 |

| Figure 4-3: USB connectors on the front panel of CPC507                                     | 25 |

| Figure 4-4: Gigabit Ethernet RJ45 connector                                                 | 26 |

| Figure 4-5: DisplayPort connector                                                           | 27 |

| Figure 4-6: LEDS on the front panel of CPC507                                               | 28 |

| Figure 4-7: CompactPCI connectors (J1 – J5 in accordance with the CompactPCI specification) | 30 |

| Figure 7-1: Assignment of navigation keys                                                   | 47 |

All information in this document is provided for reference only, with no warranty of its suitability for any specific purpose. This information has been thoroughly checked and is believed to be entirely reliable and consistent with the product that it describes. However, Fastwel accepts no responsibility for inaccuracies, omissions or their consequences, as well as liability arising from the use or application of any product or example described in this document.

Fastwel Co. Ltd. reserves the right to change, modify, and improve this document or the products described in it, at Fastwel's discretion without further notice. Software described in this document is provided on an "as is" basis without warranty. Fastwel assumes no liability for consequential or incidental damages originated by the use of this software.

This document contains information, which is property of Fastwel Co. Ltd. It is not allowed to reproduce it or transmit by any means, to translate the document or to convert it to any electronic form in full or in parts without antecedent written approval of Fastwel Co. Ltd. or one of its officially authorized agents.

Fastwel and Fastwel logo are trademarks owned by Fastwel Co. Ltd., Moscow, Russian Federation. CompactPCI is a trademark of the PCI industrial Computers Manufacturers Group. Ethernet is a registered trademark of Xerox Corporation. IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers Inc. Intel is a trademark of Intel Corporation. Pentium M and Celeron M are trademarks of Intel Corporation. Microsoft is a trademark of the Microsoft Corporation. In addition, this document may include names, company logos and trademarks, which are registered trademarks and, therefore, are property of their respective owners.

Fastwel welcomes suggestions, remarks and proposals regarding the form and the content of this Manual.

### **Ownership rights**

This document contains information that is the property of Fastwel Group. It may not be copied or transmitted by any known means, nor may it be stored in information storage and retrieval systems without the prior written consent of Fastwel Group or one of its authorized agents. The information contained in this document, to the best of our knowledge, is free from any errors, however, Fastwel Group accepts no responsibility for any inaccuracies and their consequences, as well as liability arising from the use or application of any diagram, product or example given in this document. Fastwel Group reserves the right to change and improve both this document and the product presented inside of it at its discretion without any further notice.

### Safety requirements

This Fastwel Group's product is developed and tested for the purpose of ensuring compliance to the electric safety requirements. Its design provides long-term trouble-free operation. The service life of the product can be significantly reduced due to the improper handling during unpacking and installation. Therefore, in the interests of your safety and in order to ensure proper operation of the product, you should follow the recommendations below.

## Conventions

This sign and text warn of the dangers associated with electrical discharges (> 60 V) when touching the device or any part of it. Failure to follow the precautions mentioned or prescribed in the regulations may endanger your life or health, and may result in damages to the equipment.

### Attention! Static-Sensitive Device!

This sign and text indicate that the electronic boards and their components are sensitive to static electricity, so proper care should be taken when handling this device and performing inspections to ensure its integrity and functionality.

### Attention! Hot surface!

This sign and text warn of the dangers associated with touching hot surfaces of the device.

This sign is aimed at drawing your attention to aspects of this User Manual. Failure to fully understand or ignoring these aspects may endanger your health or cause damages to the equipment.

This sign is used to text fragments that should be read carefully.

### Fastwel

### Safety requirements

This Fastwel Group product has been developed and tested to ensure compliance with electrical safety requirements. Its design provides long-term failsafe operation. Mishandling the product during unpacking and installation may significantly affect the product's life cycle. Therefore, for your own safety and for ensuring proper operation of the device, you should follow the recommendations given below.

### Rules for safe handling with high voltage

All operations with this device should only be performed by personnel with sufficient qualifications.

### Caution, High Voltage!

Before installing the board in the system, make sure that the mains power supply is off. The same also applies to the installation of expansion boards.

There is a serious risk of electric shock during installation, repairs, and maintenance of the device, so always unplug the power supply cord while carrying out of works. The same also applies to the other power supply cables.

### **Board Handling Instructions**

### Static-sensitive device!

Electronic boards and their components are sensitive to static electricity. Therefore, special attention should be given when handling these devices to ensure their safety and operability.

✓ Do not leave the board in the non-operating position without protective packaging.

✓ If possible, always work with the board in workplaces protected against static electricity. Should this not be possible, the user should remove the static charge before touching the product with their hands or tools. The best way to do so is by touching any metal part of the system enclosure.

$\checkmark$  It is especially important to observe precautions when replacing expansion boards, jumpers, etc. If the product is equipped with batteries to power the memory or real-time clock, avoid placing the board on conducting surfaces such as anti-static mats or sponges. They can cause short circuits and damage the battery and the board's conducting circuits.

### General rules of usage

In order to keep the warranty, the product must not be altered or changed in any way. Any changes and improvements unauthorized by Fastwel Group other than those contained in this User Manual or received from the technical support service of Fastwel Group in the form of a set of instructions for their implementation will void the warranty.

This device should be installed and connected only to systems that meet all necessary technical and climatic requirements. This also applies to the operating temperature range of a particular version of the board. You should also consider the temperature limits of the batteries installed on the board.

Only follow the instructions in this User Manual when performing all necessary installation and configuration operations.

Retain the original packaging for storing products in the future or to transport in case of a warranty claim. If it is necessary to transport or store the board, pack it the same way as it was packed at the time of receipt.

Proceed with extra caution when handling and unpacking the device. Follow the instructions given above and in the below chapter "Transportation, Unpacking and Storage".

### **MANUFACTURER'S WARRANTIES**

### Warranty liabilities

The manufacturer guarantees that the CPC507 Module meets the requirements of technical specifications for IMES.467444.117, provided that the Consumer complies with the operating conditions, transportation, storage, installation and mounting, set by the operational documents. The manufacturer guarantees that the products supplied by it will not show any manufacturing defects and materials used in compliance with the rules of operation and maintenance during the warranty period established at the moment. The Manufacturer's obligation under this warranty is to repair or replace, free of charge, any defective electronic component included in the returned product.

Products that failed through the Manufacturer's fault during the warranty period will be repaired free of charge. In other cases, the Consumer will be billed based on current remuneration rates and the cost of consumables.

### **Right of liability limitation**

The manufacturer is not responsible for any damages caused to the Consumer's property due to the failure of the product in the process of its use.

#### Warranty period

The warranty period for the manufacturer's products is 36 months from the date of sale (unless otherwise provided by the delivery agreement).

For customized products, the warranty period is 60 months from the date of sale (unless otherwise provided by the delivery agreement).

### Limitation of warranty obligations

The above warranty does not apply to:

- the products (including software) that have been repaired or modified by the employees who do not represent the Manufacturer. The exception is when the Consumer has made repairs or made changes to the product strictly in accordance with the instructions previously agreed and approved by the Manufacturer in writing;

- the products which have failed because of inappropriate change of a polarity sign (to the opposite one) of the power supply source, incorrect operation, transportation, storage, installation, mounting or accident.

### Procedure for returning products for repairs

In order to return the products for repairs:

- contact the Product Supplier or any official dealer of the Product Supplier for return material authorization for the product;

- attach to the returned product the fault identification report made in the form adopted by the Consumer, indicating the list of circumstances and signs of malfunction;

- place the product in the consumer packaging of the Manufacturer (antistatic bag) and cardboard packaging (box)), in which the product was delivered to the Consumer. If there is no antistatic bag, the Consumer loses the right to warranty service unilaterally;

- the Consumer pays all the expenses related to the delivery of the product to the Supplier or any official dealer of the Supplier.

# Transportation, Unpacking and Storage

### Transportation

The modules should be transported in the separate manufacturer's packaging (container), consisting of an individual antistatic packaging and a cardboard box, in closed transport (road, rail, air in heated and sealed compartments) under storage conditions 5 according to the GOST standard 15150-69 or under storage conditions 3 for sea transportation.

It is allowed to transport the modules packed in individual antistatic bags in manufacturer's group packaging (container).

Transportation of packaged modules should be carried out in accordance with the rules of transportation of goods currently valid for this type of transport.

During handling operations and transportation, the packed modules should not be subjected to sudden shocks, drops, impacts and precipitation. The packed modules should be placed on the vehicle in such a way as to preclude their further movements.

### Unpacking

Before unpacking, after transportation at negative ambient temperatures, the modules must be kept for 6 hours under storage conditions 1, in accordance with the GOST standard 15150-69.

Do not place the packed modules near any heat sources before unpacking.

When unpacking the modules, it is necessary to observe all precautions to ensure their safety, as well as marketable condition of manufacturer's consumer packaging.

When unpacking, it is necessary to check the modules for any external mechanical damages after transportation.

### Storage

Storage conditions of the modules 1 comply with the GOST standard 15150-69.

### Three Year Warranty

Fastwel Co. Ltd. (Fastwel), warrants that its standard hardware products will be free from defects in materials and workmanship under normal use and service for the currently established warranty period. Fastwel's only responsibility under this warranty is, at its option, to replace or repair any defective component part of such products free of charge.

Fastwel neither assumes nor authorizes any other liability in connection with the sale, installation or use of its products. Fastwel shall have no liability for direct or consequential damages of any kind arising out of sale, delay in delivery, installation, or use of its products.

If a product should fail through Fastwel's fault during the warranty period, it will be repaired free of charge. For out of warranty repairs, the customer will be invoiced for repair charges at current standard labor and materials rates.

Warranty period for Fastwel products is 36 months since the date of purchase.

For customized products, the warranty period is 60 months from the date of sale (unless otherwise provided by the delivery agreement).

#### The warranty set forth above does not extend to and shall not apply to:

- 1. Products, including software, which have been repaired or altered by other than Fastwel personnel, unless Buyer has properly altered or repaired the products in accordance with procedures previously approved in writing by Fastwel.

- 2. Products, which have been subject to power, supply reversal, misuse, neglect, accident, or improper installation.

#### Returning a product for repair

- 1. Apply to Fastwel Company or to any of the Fastwel's official representatives for the Product Return Authorization.

- 2. Attach a failure inspection report with a product to be returned in the form, accepted by customer, with a description of the failure circumstances and symptoms.

- 3. Carefully package the product in the antistatic bag, in which the product had been supplied. Failure to package in antistatic material will VOID all warranties. Then package the product in a safe container for shipping.

- 4. The customer pays for shipping the product to Fastwel or to an official Fastwel representative or dealer.

# 1 Introduction

### 1.1 System overview

The CPC507 (IMES.467444.117) CPU module (hereinafter referred to as the Device or the Product) presented in this User Manual is manufactured in CompactPCI (CPCI) form-factor and supports the PCI architecture. This allows you to work with a wide range of equipment. For the information on the CompactPCI standard, please refer to the relevant specifications for PCI and CompactPCI Standards. For more information on these standards and their use, please visit the official website of the PCI Industrial Computer Manufacturers Group (PICMG) at: <a href="http://www.picmg.org/">http://www.picmg.org/</a>.

### 1.2 General Description of the Module

The CPC507 CPU module, implemented in accordance with the 6U CompactPCI standard, expands the line of Fastwel 6U modules. The most important feature of this module is the availability of two platforms for installation of PMC / XMC mezzanine modules. By using a single-chip solution based on AMD FP5 APU (Ryzen Embedded V-Series) SoC, together with 2 mezzanine modules, CPC507 can be used in compact and cost-effective computing systems.

The Ryzen Embedded platform is an up-to-date solution from AMD (launched in 2018, availability period: 10 years) based on the 14 nm technology. The System on a Chip (SoC) supports modern high-speed interfaces and also has an integrated graphics core with a large number of high-resolution digital video outputs.

### **1.3 Module versions**

Module versions are specified in the Table 1-1 below.

### Table 1-1 – Versions of CPC507

| Name                 | Conventional name | Ordering name | Note                                                                                                                                                                                                   |

|----------------------|-------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPC507 CPU<br>Module | 000507            | CPC507-01     | AMD Ryzen Embedded V1404I processor 25W 4 cores, 16GB<br>DDR4 SDRAM with ECC support, 3x LAN 10/100/1000 Mb, 3x<br>USB 3.1, DisplayPort, CFast, 64 GB 3D NAND Flash, <b>from -</b> 40<br>°C to +70 °C. |

|                      | CPC507            | CPC507-02     | AMD Ryzen Embedded V1404I processor 15 W 4 cores, 8 GB<br>DDR4 SDRAM with ECC support, 3 x LAN 10/100/1000 Mb, 3<br>x USB 3.1, DisplayPort, CFast, 64 GB 3D NAND Flash, from -<br>40 °C to +85 °C.     |

Note – Application of conformal coating is available. When ordered, the -COATED option is added to the version name, for example CPC507-01-COATED.

# 2 General Information

### 2.1 General Features of CPC507

### • Processor AMD Ryzen Embedded V1404I SoC APU:

- 4 x cores x64, 8 x threads;

- 8 x graphics cores;

- 6 MB cache;

### • RAM:

- DDR4-2400 SDRAM with ECC support:

- 16 GB (for CPC507-01);

- 8 GB (for CPC507-02).

### • Video Output:

- DisplayPort (4096x2160@60Hz) interface, routed to the front panel;

### • PCI Bus:

- Routed to the CompactPCI J1/J2 connectors;

- 64bit/66MHz;

- Implemented on the bridge PCIe->PCI-X PI7C9X130;

- Operation in the peripheral slot (Non-transparent Bridge mode).

### • PCle Bus:

PCIe Gen3 (up to 8GT/s) is routed to the P15 XMC connector with support of up to x8 devices;

Possibility to use link x8 in the 2x4 mode (configurable in BIOS), links x4 are routed to the P15 XMC1 and XMC2 connectors;

### • FRAM:

- Volume 32 KB;

### • Integrated SATA SSD:

- Capacity 64 GB 3D NAND Flash (Pseudo-SLC);

- SATA III 6 Gbps interface;

### • CFast drive:

- Speed SATA III 6 Gbps interface;

### • SPI interface:

- FRAM support;

### • 3 x LAN ports 10/100/1000 Mb on PCIe x4 Gen2:

- 2 x channels are routed to the backplane (PICMG 2.16);

- 1 x channel is routed to the front panel;

- Intel® Ethernet Controller I350 is used;

- USB ports:

- Support of USB 2.0 (480 Mb/sec), USB 3.1 Gen 1 (5 Gb/sec);

- Connection of up to 3 x devices via connectors on the front panel (USB 3.1 Gen 1);

### • Real Time Clock:

- Power is supplied from the CR2032 (3V) lithium battery;

### • Watchdog Timer:

- 30 µs to 512 s with program control option;

#### • Hardware monitor:

- Implemented via the SMBus interface;

- Monitoring of up to 7 power supply voltages;

- Monitoring the board temperature at two points;

#### • Support of XMC/PMC expansion boards:

- Support of 2 x PMC/XMC modules;

- PCI-X 64bit/66MHz bus is routed to the P1-P4 PMC1 and PMC2 connectors;

- PMC I/O P4 is routed to RIO for the both mezzanines (PICMG PMC on CompactPCI R1.0 Specification);

- PCIe x8 Gen3 Bus is routed to the P15 XMC1 (ANSI/VITA 42.3, XMC: PCI Express Protocol Layer) connector, can be used in the x4 mode for 2 x mezzanines.

#### • LEDs:

- Board start diagnostics LED;

- LED for accessing SATA drives;

- LED for indication of processor overheating;

- Two program-controlled LEDs (User LEDs);

### • Software compatibility:

- Linux Debian 10;

- Astra Linux Special Edition, "Smolensk" release v1.5, v1.6;

- Microsoft Windows 10 IoT Enterprise 64bit.

### • MTBF:

- Min. 50,000 hours;

### 2.2 Compatibility with the PICMG/VITA standards

The CPC507 module is compatible with the following PICMG/VITA standards:

- PICMG 2.0 CompactPCI R3.0 Specification;

- PICMG 2.3 PMC on CompactPCI R1.0 Specification;

- PICMG 2.16 CompactPCI Packet Switching Backplane R1.0 Specification;

- ANSI/VITA 42.0 XMC: Switched Mezzanine Card Base Specification;

- ANSI/VITA 42.3 XMC: PCI Express Protocol Layer;

- ANSI/VITA 30.1 2mm Connector Practice for Conduction Cooled Euroboards;

- ANSI/VITA 39 PCI-X for PMC and Processor PMC;

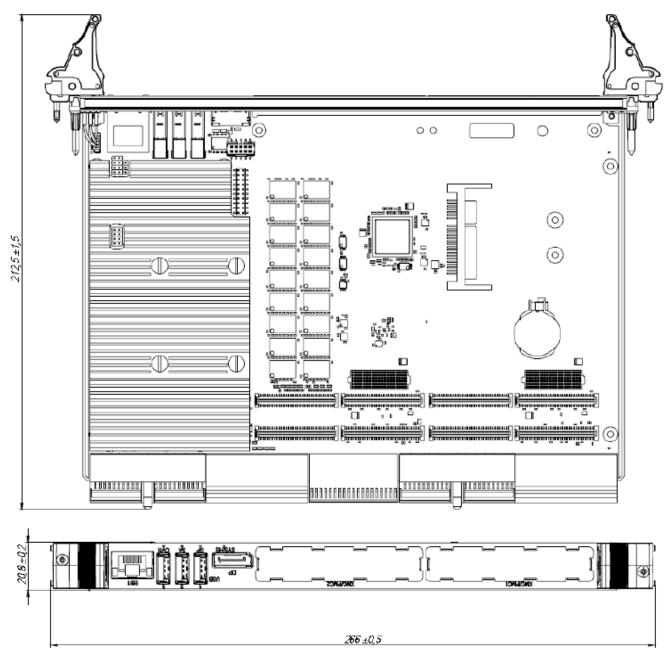

### 2.3. Device dimensions

Figure 2-1: Device dimensions

### 2.4. Delivery checklist

The complete delivery checklist for CPC507 is specified in the Table 1-2.

#### Table 2-1: Delivery checklist

| Designation                           | Name                                                                                                                     | Number | Note |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------|------|

| IMES.467444.117<br>IMES.467444.117-01 | CPC507-01 CPU Module<br>CPC507-02 CPU Module                                                                             | 1 pcs. |      |

|                                       |                                                                                                                          |        |      |

| IMES.467941.057                       | An installation kit consisting of:<br>- locking mechanism IMES.741124.233 - 1 pcs;<br>- screw DIN7985-M2,5x6-A2 - 2 pcs. | 1 pcs. |      |

| IMES.421945.071-16                    | Packaging                                                                                                                | 1 pcs. |      |

### 2.5 Operational conditions

The product must be remain functional under climatic and mechanical effects given in Table 1-3.

| Table 2-2: Operational ranges of external infl | uencing factors |

|------------------------------------------------|-----------------|

|------------------------------------------------|-----------------|

| Influencing factor                | Characteristics of the influencing factor                                            | Value of the influencing factor    |

|-----------------------------------|--------------------------------------------------------------------------------------|------------------------------------|

| 1. Sinusoidal vibration           | Acceleration amplitude, m/s <sup>2</sup> (g)                                         | 20 (2)                             |

|                                   | Frequency range, Hz                                                                  | 10-500                             |

|                                   | Acceleration amplitude, m/s <sup>2</sup> (g)                                         | 300 (30)                           |

| 2. Single acting mechanical shock | Duration of shock acceleration, ms                                                   | 11                                 |

|                                   | Acceleration amplitude, m/s <sup>2</sup> (g)                                         | 100 (10)                           |

| 3. Repeated mechanical shock      | Duration of shock acceleration, ms                                                   | 11                                 |

| Influencing factor                | Characteristics of the influencing factor                                            | Value of the influencing factor    |

|                                   | Number of shocks                                                                     | 1000                               |

| 4. Ambient temperature            | Measuring range, °C <ul> <li>version CPC507-01</li> <li>version CPC507-02</li> </ul> | From -40 to +70<br>From -40 to +85 |

| 5. Cyclic damp heat*              | Temperature, °C                                                                      | 55                                 |

|                                              | Relative humidity, %                       | 93                              |

|----------------------------------------------|--------------------------------------------|---------------------------------|

| * - only for versions with conformal coating | (additional option, when ordering – COATED | ) is added to the product name) |

### 2.6 Product labeling

Product labelling shall contain:

- Name and trademark of the manufacturer;

- Product name;

- Factory number of the product;

- Product's version.

- The package labelling shall contain:

- Product name;

- Product version;

- Factory number of the product.

### 2.7 Packaging information

The CPC507 Module is supplied in a box of the following size: 350x260x70 mm. Packaged weight of the device – no more than 0.8 kg.

### Note

Keep the module's anti-static bag and consumer packaging in their original form until the end of the warranty period.

# **3 Design and operation**

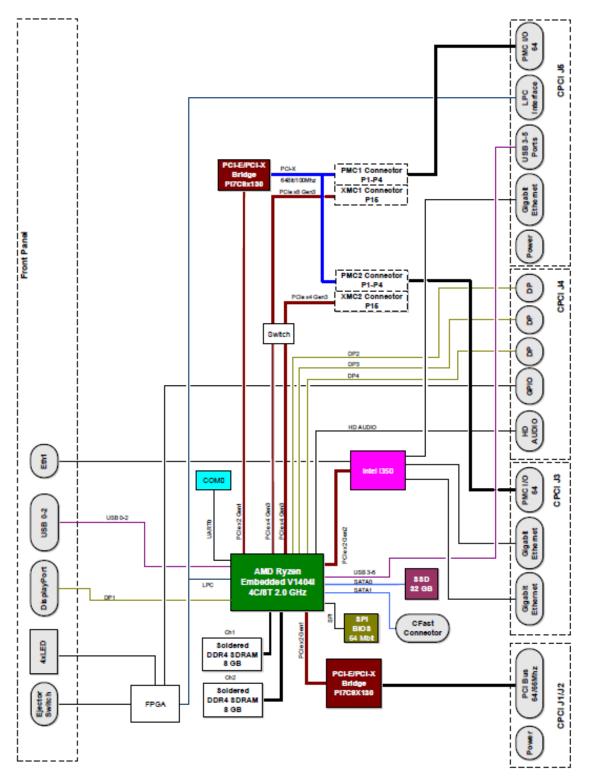

### 3.1 Block diagram

The block diagram is specified in Figure 3-1 below.

Fig. 3-1 – Block diagram of the device

### 3.2 Specific performance features of functional nodes

### AMD Ryzen Embedded SoC APU

64-bit AMD CPU, manufactured on 14nm technology node, offering TDP of 25W and an industrial operating temperature range (from -40 to + 105°C).

This CPU is a single-chip solution that combines 4 x AMD "Zen" processing cores, a 64-bit dualchannel DDR4 SDRAM memory controller (up to 32 GB, 2400 MHz) and ECC support, the up-todate AMD Radeon Vega graphics subsystem with 2D/3D acceleration, an I/O subsystem (PCIe, USB, SATA) and a set of standard hardware platform support (RTC, UART, Timers, GPIO).

The processor is implemented in the FP5-BGA1140 enclosure, 35x25mm.

#### DDR4 SDRAM

The board can have 18 x DDR4 2400 MHz SDRAM chips installed (soldered) on it with a total capacity of up to 16GB. (18 x 8 GB x 8). The operating mode is two-channel, with ECC support.

#### RTC, NVRAM

The real time clock is integrated into the SoC. The clock operation in the power-off state is ensured by a CR2032 lithium battery installed on the board. BIOS settings are stored in FRAM non-volatile memory.

### FRAM

There is a non-volatile memory of 32 KB (Ramtron, FM25V02, SPI), which is required for storing user data (used as a replacement for standard non-volatile RAM). The manufacturer guarantees 100 trillion read/write cycles, which in this type of application corresponds to ~ 340 years of operation (in the case of a continuous cyclic write/ read procedure).

### BGA SSD

The board is equipped with a 64 GB SATA III 6 Gbps SSD in a TFBGA 16x20mm Jedec MO-276 enclosure.

#### Ethernet

The board has 3 x integrated Gigabit Ethernet interfaces. One is routed to the front panel, the other two – to the backplane (PICMG 2.16). The interfaces are implemented on the high-speed Intel® Ethernet Controller I350.

#### USB

The board has 3 x USB 3.1 Gen 1 channels routed to type A USB connectors on the front panel.

#### CFast

The CFast is used for connecting appropriate drives. SATA III (6 Gbps) speed is supported.

#### DisplayPort

The interface is designed to connect digital monitors with a resolution up to 4096x2160@60Hz.

#### PCI Express

The PCIe Gen3 bus is routed to the P15 XMC1 connector in accordance with the ANSI/VITA 42.3 standard. The interface enables you to connect XMC expansion modules with a set of links x1, x2, x4, x8. A PCIe x4 link is routed to the P15 XMC2 connector. It can be used if the link on the XMC1 is narrowed down to x4.

#### PCI

The PCI bus is implemented on the Pericom PI7C9X130 reversible bridge chip connected to the PCIe x2 bus. The following operating modes are supported: PCI 32bit/33MHz, PCI 64bit/66MHz. The operation both in the system and in the peripheral slot is supported.

### COM0

The debug COM port is routed to the IDC XP2 connector on the board.

### LEDs

The LEDs for indication of startup diagnostics, drive activities, overheating as well as User LEDs are routed to the front panel. The diagnostics LED enables you to distinguish 4 board states: power OFF, power ON, BIOS start, BIOS shutdown (operating system start). The drive activities LED informs about the activities of the SATA interfaces. Two program-controlled LEDs are intended for user needs.

### Watchdog

The module is equipped with a watchdog timer, which is built into the supervisor's microchip and has an adjustable actuation interval (30.52µs - 512s).

### Jumpers

The board has a switch for resetting BIOS to default settings.

### 3.3 System expansion options

The number of interfaces routed from the CPC507 module can be increased by installing 2 x XMC/PMC expansion modules.

### 3.3.1 PMC/XMC Modules

PMC/XMC interface of the CPC507 board supports two expansion modules of the XMC/PMC standard, which ensures an easy and flexible adaptation of CPC507 in accordance with the requirements of various applications.

### 3.4 Using the module in the CPCI system

| Characteristics                                      | Note                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation in the system slot<br>as the System Master | The CPC507 module is designed for the use as the System Master. In this capacity, it can interrelate with seven peripheral boards via a 64-bit 33/66 MHz bus.                                                                                                                                                                              |

| Operation in the peripheral slot of the system       | The CPC507 module, when installed in the system's peripheral slot, is connected to the PCI bus through the "nontransparent" bridge. The CPC507 is powered from the backplane and can operate in the PICMG 2.16 packet switching mode (if the system supports the PICMG 2.16 standard) with support of up to 2 x Gigabit Ethernet channels. |

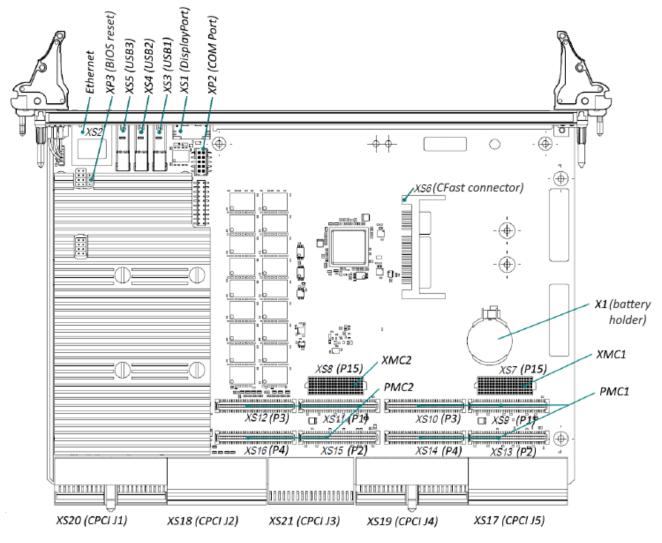

### 3.5 Location of main components

Figure 3-2: Location of the main components of CPC507

The appearance of the module versions may slightly differ from the one shown in this figure.

## 4 Intended use

### 4.1 Module Interfaces

### 4.1.1 XMC interface

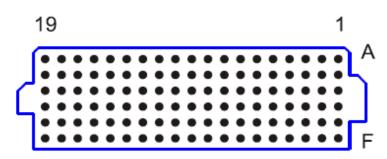

For XMC expansion modules, the CPC507 board is equipped with XS7 (P15) and XS8 (P15) connectors.

Figure 4-1: XMC XS7 (P15) and XS8 (P15) connectors

Below you can find the pinout tables for XMC connectors.

|     | P15   |       |           |       |       |         |

|-----|-------|-------|-----------|-------|-------|---------|

| Pin | Α     | В     | С         | D     | Е     | F       |

| 1   | RX0+  | RX0-  | +3.3V     | RX1+  | RX1-  | +5V     |

| 2   | GND   | GND   | NC        | GND   | GND   | PCIRST# |

| 3   | RX2+  | RX2-  | +3.3V     | RX3+  | RX3-  | +5V     |

| 4   | GND   | GND   | NC        | GND   | GND   | RSTO#   |

| 5   | RX4+  | RX4-  | +3.3V     | RX5+  | RX5-  | +5V     |

| 6   | GND   | GND   | NC        | GND   | GND   | +12V    |

| 7   | RX6+  | RX6-  | +3.3V     | RX7+  | RX7-  | +5V     |

| 8   | GND   | GND   | NC        | GND   | GND   | -12V    |

| 9   | NC    | NC    | NC        | NC    | NC    | +5V     |

| 10  | GND   | GND   | NC        | GND   | GND   | GA0     |

| 11  | TX0+  | TX0-  | GA1       | TX1+  | TX1-  | +5V     |

| 12  | GND   | GND   | GND       | GND   | GND   | PRSNT#  |

| 13  | TX2+  | TX2-  | +3.3V_SBY | TX3+  | TX3-  | +5V     |

| 14  | GND   | GND   | GA2       | GND   | GND   | MSDA    |

| 15  | TX4+  | TX4-  | NC        | TX5+  | TX5-  | +5V     |

| 16  | GND   | GND   | MVMRO     | GND   | GND   | MSCL    |

| 17  | TX6+  | TX6-  | NC        | TX7+  | TX7-  | NC      |

| 18  | GND   | GND   | NC        | GND   | GND   | NC      |

| 19  | CLK0+ | CLK0- | NC        | WAKE# | ROOT# | NC      |

### 4.1.2. PMC interface

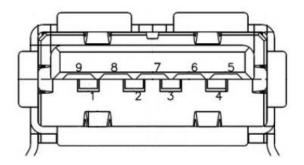

The PMC expansion modules are plugged into XS9 (P1), XS10 (P3), XS13 (P2) and XS14 (P4) connectors for PMC1 and XS11 (P1), XS12 (P3), XS15 (P2), XS16 (P4) connectors for PMC2.

|   | 1 |

|---|---|

|   |   |

|   |   |

|   |   |

| — | 2 |

Figure 4-2: Connectors PMC XS10 (P3), XS11 (P1), XS12 (P3) and XS13 (P2)

The PMC connectors have 64-bit PCI bus lines routed to them. The user-defined I/O signals are supported and are routed to J5 and J3 CompactPCI connectors.

The PMC interface complies with the ANSI/VITA 39 specification, which defines the PCI-X electrical interface for the boards of the Common Mezzanine Card (CMC) form-factor. CPC507 allows operation of the 3.3V PCI bus.

#### Note:

The PMC I/O signals are routed to the J5, J3 CompactPCI connectors. Their pin assignments can be found in this chapter below.

The table with the PMC connector pinouts can be found on the next page.

| Number of pin<br>XS9(P1)/XS11( | Function     | Number of pin<br>XS13(P2)/XS | Function              | Number of pin<br>XS10(P3)/XS12 |              | Number of pin         | Function |

|--------------------------------|--------------|------------------------------|-----------------------|--------------------------------|--------------|-----------------------|----------|

| P1)                            |              | 15(P2)                       |                       | (P3)                           | Function     | XS14(P4)/<br>XS16(P4) |          |

| P1_1                           | NC           | P2_1                         | +12V                  | P3_1                           | NC           | P4_1                  | PMC_I/O  |

| P1_2                           | -12V         | P2_2                         | NC                    | P3_2                           | GND          | P4_2                  | PMC_I/O  |

| P1_3                           | GND          | P2_3                         | NC                    | P3_3                           | GND          | P4_3                  | PMC_I/O  |

| P1_4                           | INTD#        | P2_4                         | NC                    | P3_4                           | C_BE7#       | P4_4                  | PMC_I/O  |

| P1_5                           | INTE#        | P2_5                         | NC                    | P3_5                           | C_BE6#       | P4_5                  | PMC_I/O  |

| P1_6                           | INTF#        | P2_6                         | GND                   | P3_6                           | C_BE5#       | P4_6                  | PMC_I/O  |

| P1_7                           | NC           | P2_7                         | GND                   | P3_7                           | C_BE4#       | P4_7                  | PMC_I/O  |

| P1_8                           | VCC          | P2_8                         | NC                    | P3_8                           | GND          | P4_8                  | PMC_I/O  |

| P1_9                           | INTG#        | P2_9                         | NC                    | P3_9                           | VIO          | P4_9                  | PMC_I/O  |

| P1_10                          | NC           | P2_10                        | NC                    | P3_10                          | PAR64        | P4_10                 | PMC_I/O  |

| P1_11                          | GND          | P2_11                        | PULL_UP               | P3_11                          | AD63         | P4_11                 | PMC_I/O  |

| P1_12                          | NC           | P2_12                        | +3,3V                 | P3_12                          | AD62         | P4_12                 | PMC_I/O  |

| P1_13                          | PCICLK       | P2_13                        | PCIRST#               | P3_13                          | AD61         | P4_13                 | PMC_I/O  |

| P1_14                          | GND          | P2_14                        | PULL_DOWN             | P3_14                          | GND          | P4_14                 | PMC_I/O  |

| P1_15                          | GND          | P2_15                        | +3,3V                 | P3_15                          | GND          | P4_15                 | PMC_I/O  |

| P1_16                          | GNT#         | P2_16                        | PULL_DOWN             | P3_16                          | AD60         | P4_16                 | PMC_I/O  |

| P1_17                          | REQ#         | P2_17                        | PME#                  | P3_17                          | AD59         | P4_17                 | PMC_I/O  |

| P1_18                          | VCC          | P2_18                        | GND                   | P3_18                          | AD58         | P4_18                 | PMC_I/O  |

| P1_19                          | VIO          | P2_19                        | AD30                  | P3_19                          | AD57         | P4_19                 | PMC_I/O  |

| P1_20                          | AD31         | P2_20                        | AD29                  | P3_20                          | GND          | P4_20                 | PMC_I/O  |

| P1_21                          | AD28         | P2_21                        | GND                   | P3_21                          | VIO          | P4_21                 | PMC_I/O  |

| P1_22                          | AD27         | P2_22                        | AD26                  | P3_22                          | AD56         | P4_22                 | PMC_I/O  |

| P1_23                          | AD25         | P2_23                        | AD24                  | P3_23                          | AD55         | P4_23                 | PMC_I/O  |

| P1_24                          | GND          | P2_24                        | +3,3V                 | P3_24                          | AD54         | P4_24                 | PMC_I/O  |

| P1_25                          | GND          | P2_25                        | IDSEL(AD19/AD21)      | P3_25                          | AD53         | P4_25                 | PMC_I/O  |

| P1_26                          | C_BE3#       | P2_26                        | AD23                  | P3_26                          | GND          | P4_26                 | PMC_I/O  |

| P1_27                          | AD22         | P2_27                        | +3,3V                 | P3_27                          | GND          | P4_27                 | PMC_I/O  |

| P1_28                          | AD21         | P2_28                        | AD20                  | P3_28                          | AD52         | P4_28                 | PMC_I/O  |

| P1_29                          | AD19         | P2_29                        | AD18                  | P3_29                          | AD51         | P4_29                 | PMC_I/O  |

| P1_30                          | VCC          | P2_30                        | GND                   | P3_30                          | AD50         | P4_30                 | PMC_I/O  |

| P1_31                          | VIO          | P2_31                        | AD16                  | P3_31                          | AD49         | P4_31                 | PMC_I/O  |

| P1_32                          | AD17         | P2_32                        | C_BE2#                | P3_32                          | GND          | P4_32                 | PMC_I/O  |

| P1_33                          | FRAME#       | P2_33                        | GND                   | P3_33                          | GND          | P4_33                 | PMC_I/O  |

| P1_34                          | GND          | P2_34                        | IDSELB(AD20/AD2<br>2) | P3_34                          | AD48         | P4_34                 | PMC_I/O  |

| P1_35                          | GND          | P2_35                        | Z)<br>TRDY#           | P3_35                          | AD47         | P4_35                 | PMC_I/O  |

| <br>P1_36                      | IRDY#        | P2_36                        | +3,3V                 | <br>P3_36                      | AD46         | <br>P4_36             | PMC_I/O  |

| P1_37                          | DEVSEL#      | P2_37                        | GND                   | P3_37                          | AD45         | P4_37                 | PMC_I/O  |

| P1_38                          | VCC          | P2_38                        | STOP#                 | P3_38                          | GND          | P4_38                 | PMC_I/O  |

| P1_39                          | GND          | P2_39                        | PERR#                 | P3_39                          | VIO          | P4_39                 | PMC_I/O  |

| P1_40                          | LOCK#        | P2_40                        | GND                   | P3_40                          | AD44         | P4_40                 | PMC_I/O  |

| P1_41                          | SCL          | P2_41                        | +3,3V                 | P3_41                          | AD43         | P4_41                 | PMC_I/O  |

| P1_42                          | SDA          | P2_42                        | SERR#                 | P3_42                          | AD42         | P4_42                 | PMC_I/O  |

| P1_43                          | PAR          | P2_43                        | C_BE1#                | P3_43                          | AD41         | P4_43                 | PMC_I/O  |

| P1_44                          | GND          | P2_44                        | GND                   | P3_44                          | GND          | P4_44                 | PMC_I/O  |

| P1_45                          | VIO          | P2_44<br>P2_45               | AD14                  | P3_45                          | GND          | P4_45                 | PMC_I/O  |

| P1_45                          | AD15         | P2_46                        | AD14<br>AD13          | P3_46                          | AD40         | P4_45<br>P4_46        | PMC_I/O  |

| P1_40                          | AD13         | P2_40<br>P2_47               | M66EN                 | P3_40                          | AD40<br>AD39 | P4_40<br>P4_47        | PMC_I/O  |

| P1_47<br>P1_48                 | AD12<br>AD11 |                              | AD10                  | P3_47<br>P3_48                 | AD39<br>AD38 |                       | PMC_I/O  |

|                                |              | P2_48                        |                       |                                |              | P4_48                 |          |

| P1_49                          | AD9          | P2_49                        | AD8                   | P3_49                          | AD37         | P4_49                 | PMC_I/O  |

| P1_50                          | VCC          | P2_50                        | +3,3V                 | P3_50                          | GND          | P4_50                 | PMC_I/O  |

| P1_51                          | GND          | P2_51                        | AD7                   | P3_51                          | GND          | P4_51                 | PMC_I/O  |

| P1_52                          | C_BE0#       | P2_52                        | NC                    | P3_52                          | AD36         | P4_52                 | PMC_I/O  |

| P1_53                          | AD6          | P2_53                        | +3,3V                 | P3_53                          | AD35         | P4_53                 | PMC_I/O  |

| P1_54                          | AD5          | P2_54                        | NC                    | P3_54                          | AD34         | P4_54                 | PMC_I/O  |

Table 4-2: PMC connector pin assignment

| P1_55 | AD4    | P2_55 | NC      | P3_55 | AD33 | P4_55 | PMC_I/O |

|-------|--------|-------|---------|-------|------|-------|---------|

| P1_56 | GND    | P2_56 | GND     | P3_56 | GND  | P4_56 | PMC_I/O |

| P1_57 | VIO    | P2_57 | NC      | P3_57 | VIO  | P4_57 | PMC_I/O |

| P1_58 | AD3    | P2_58 | EREADY  | P3_58 | AD32 | P4_58 | PMC_I/O |

| P1_59 | AD2    | P2_59 | GND     | P3_59 | NC   | P4_59 | PMC_I/O |

| P1_60 | AD1    | P2_60 | RSTOUT# | P3_60 | NC   | P4_60 | PMC_I/O |

| P1_61 | AD0    | P2_61 | ACK64#  | P3_61 | NC   | P4_61 | PMC_I/O |

| P1_62 | VCC    | P2_62 | +3,3V   | P3_62 | GND  | P4_62 | PMC_I/O |

| P1_63 | GND    | P2_63 | GND     | P3_63 | GND  | P4_63 | PMC_I/O |

| P1_64 | REQ64# | P2_64 | NC      | P3_64 | NC   | P4_64 | PMC_I/O |

#### 4.1.3 SATA interface

The CPC507 module has two interfaces for connecting drives: one interface is routed to the CFast connector (XS6); the second interface is used for connection of the integrated SSD.

The XS6 connector (located on the top side of the CPC507 board, see Figure 3-2: Location of the main components of CPC507) enables installing a CFast drive on the CPC507 module together with the PMC/XMC expansion module.

Table 4-3: Assignment of SATA XS6 connector pins

|     | XS6        |

|-----|------------|

| Pin | Assignment |

| S1  | GND        |

| S2  | A+         |

| S3  | A-         |

| S4  | GND        |

| S5  | B-         |

| S6  | B+         |

| S7  | GND        |

| P1  | GND        |

| P2  | GND        |

| P3  | NC         |

| P4  | NC         |

| P5  | NC         |

| P6  | NC         |

| P7  | GND        |

| P8  | NC         |

| P9  | NC         |

| P10 | NC         |

| P11 | NC         |

| P12 | NC         |

| P13 | +3.3V      |

| P14 | +3.3V      |

| P15 | GND        |

| P16 | GND        |

| P17 | CDO        |

Subparagraph 5.6 describes how to install a CFast drive on a CPC507 module.

### 4.1.4 COM port

The module has a COM0 (XP2) debug connector for connecting a cable with an IDC connector. The pin assignment of the connector is given in the table below:

#### Table 4-4: Assignment of XP2 connector pins

|     | XP2        |

|-----|------------|

| Pin | Assignment |

| 1   | NC         |

| 2   | NC         |

| 3   | RXD        |

| 4   | RTS        |

| 5   | TXD        |

| 6   | CTS        |

| 7   | NC         |

| 8   | NC         |

| 9   | GND        |

| 10  | GND        |

### 4.1.5 Connectors on the front panel of CPC507

### 4.1.5.1 USB interfaces

CPC507 has 3 x USB3.1 Gen 1 ports located on the front panel. The following modes are supported: high-speed, full-speed, and low-speed. USB 2.0 in the high-speed mode enables data transfer at the rates up to 480 Mb/sec, USB 3.1 Gen1 - up to 5 Gb/sec.

The USB power supply is protected by a 1500mA automatic fuse.

Figure 4-3: USB connectors on the front panel of CPC507

| Pin | Circuit    | Function                 |

|-----|------------|--------------------------|

| 1   | VBus       | +5V Power                |

| 2   | USB D-     | Differential USB-        |

| 3   | USB D+     | Differential USB+        |

| 4   | GND        | Ground for power return  |

| 5   | StdA_SSRX- | SuperSpeed RX-           |

| 6   | StdA_SSRX+ | SuperSpeed RX+           |

| 7   | GND_DRAIN  | Ground for signal return |

| 8   | StdA_SSTX- | SuperSpeed TX-           |

| 9   | StdA_SSTX+ | SuperSpeed TX+           |

Table 4-5: Assignment of USB connector pins on the front panel of CPC507

#### 4.1.5.2 Gigabit Ethernet interface

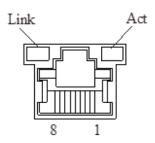

The front panel of CPC507 is equipped with the 10Base-T/100Base-TX/1000Base-T Ethernet port based on the Gigabit Ethernet I350 network controller.

Figure 4-4: Gigabit Ethernet RJ45 connector

The interface provides automatic detection of transmission speed and switching between 10Base-T, 100Base-TX and 1000Base-T data transmission modes.

Table 4-6: Assignment of Gigabit Ethernet connector pins

| Pin | 10Ba | ase-T  | 100Ba | ise-TX | 1000E | Base-T |

|-----|------|--------|-------|--------|-------|--------|

| Pin | I/O  | Signal | I/O   | Signal | I/O   | Signal |

| 1   | 0    | TX+    | 0     | TX+    | I/O   | BI_DA+ |

| 2   | 0    | TX–    | 0     | TX–    | I/O   | BI_DA- |

| 3   | I    | RX+    | I     | RX+    | I/O   | BI_DB+ |

| 4   | -    | -      | -     | -      | I/O   | BI_DC+ |

| 5   | -    | -      | -     | -      | I/O   | BI_DC- |

| 6   | I    | RX–    | I     | RX–    | I/O   | BI_DB- |

| 7   | _    | _      | _     | _      | I/O   | BI_DD+ |

| 8   | _    | _      | _     | _      | I/O   | BI_DD- |

#### LEDs indicating the state of Ethernet channel

The green and orange "Link" LED is ON, when the line is connected.

The green LED is on if a 100 Mb/sec. link is set, the orange LED is on if a 1000 Mb/sec. link is set.

The yellow "Act" LED is on when the computer is receiving or sending packets through the RJ45 connector.

#### 4.1.5.3 DisplayPort

The DisplayPort connector on the front panel of the CPC507 is designed for connecting digital monitors with resolution up to 4096x2160@60Hz. The output also makes it possible to connect DVI-D monitors via a passive adapter and VGA and other monitor types via an active adapter.

Figure 4-3: DisplayPort connector

Table 4-7: Assignment of XS1 DisplayPort connector pins of the CPC507 module

| XS1 (DP) |            |  |  |

|----------|------------|--|--|

| Pin      | Assignment |  |  |

| 1        | LANE0+     |  |  |

| 2        | GND        |  |  |

| 3        | LANE0-     |  |  |

| 4        | LANE1+     |  |  |

| 5        | GND        |  |  |

| 6        | LANE1-     |  |  |

| 7        | LANE2+     |  |  |

| 8        | GND        |  |  |

| 9        | LANE2-     |  |  |

| 10       | LANE3+     |  |  |

| 11       | GND        |  |  |

| 12       | LANE3-     |  |  |

| 13       | AUX_EN#    |  |  |

| 14       | CONFIG2    |  |  |

| 15       | AUX+       |  |  |

| 16       | GND        |  |  |

| 17       | AUX-       |  |  |

| 18       | HP_DETECT  |  |  |

| 19       | GND        |  |  |

| 20       | +3.3V      |  |  |

### 4.1.6 LEDs on the front panel of CPC507

The front panel of CPC507 is equipped with the following LEDs:

The diagnostics LED (SYS/HS, two-color green and blue) enables you to distinguish 4 states of the board: power off, power on, BIOS start, BIOS shutdown (operating system start). The state of the SYS LED is shown in the below Table 4.8. The state of the SYS LED is shown in the below table:

#### Table 4-8: State of the SYS LED of the CPC507 module

| SYS LED              | State                                              |

|----------------------|----------------------------------------------------|

| Off                  | The power is not supplied to the module            |

| Blinking green ~8 Hz | Processor is running BIOS                          |

| Blinking green ~1 Hz | Processor is executing POST procedures             |

| Solid green          | POST procedure is complete, OS boot is in progress |

- The program-controlled GP LED is designed for user needs (two-color, red and green), see subparagraph 4.4 SPI Controller / LEDs / GPIO. The red GP LED can alert the user that the device is malfunctioning (see section 8 Troubleshooting).

- The indicator for drive activity (SA, orange) informs of the activity of the SATA interfaces.

- Overheating (OVH) LED.

Figure 4-6: LEDS on the front panel of CPC507

### 4.1.7 Using the module in CompactPCI system

The CPC507 module has a flexible CompactPCI interface. If the board is installed into the system slot, then the PCIE-PCI bridge operates in the PCI bus master mode, and if the board is installed into the peripheral slot, the bridge operates in the "non-transparent" mode.

#### 4.1.7.1 Operation in system slot (System Master)

Being in the system slot, the CPC507 module can exchange information with all other CompactPCI boards through the 64-bit Pericom PI7C9X130 PCIE-PCI reversible bridge operating at 33/66 MHz.

The module supports a maximum of 7 x CompactPCI devices via the passive backplane (for 33 MHz), 6 x devices can operate in BUS Master Mode.

The module supports 3.3V and 5V PCI bus levels.

The module fully complies with the PCI Local Bus Specification Rev. 3.0.

### 4.1.7.2 Operation in peripheral slot (Slave Mode)

In the peripheral slot, the bridge operates in the "non-transparent" mode, while there is a possibility of data exchange via the PCI bus

### 4.1.7.3 Packet Switching Backplane PICMG 2.16

2 x Gigabit Ethernet ports are available on the XS21 connector of the device in accordance with the PICMG specification for CompactPCI Packet Switching Backplane Specification PICMG 2.16, version 1.0. By the CompactPCI Packet Switching Backplane these ports are connected with special-purpose Ethernet hub fabric slots.

These Ethernet slots can be used with any slots that support installation of end devices of the PICMG 2.16 standard (Node slots).

#### 4.1.7.4 Ejector's lever button

The button on the lower ejector's lever can be used to turn off or reset the device. If you press the button quickly (holding it down for less than 3 seconds) restarts the device. If you hold down for a longer period (e.g. when the ejector's lever is pulled down) this initiates the device shutdown procedure. The lever operation mode can be changed in the BIOS Setup.

#### 4.1.8 Compact PCI connectors

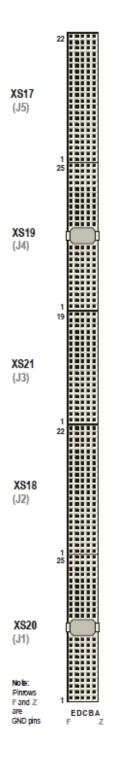

The complete set of CompactPCI connectors includes 5 connectors J1 through J5. Their purposes are described below:

✓ J1 and J2 - 64- 64-bit CompactPCI interface, including PCI bus signals, arrangement of bus access, timing, and power;

- ✓ J3 provides interface Rear I/O and PICMG 2.16 functions;

- ✓ J4 and J5 provide additional Rear I/O interface functions.

The device is designed in accordance with the CompactPCI bus architecture. The CompactPCI standard is electrically identical to the local PCI bus, but these systems have been improved in order to allow them to be used in harsh industrial environments with an increased number of expansion slots.

Figure 4-7: CompactPCI connectors (J1 – J5 in accordance with the CompactPCI specification)

#### 4.1.8.1 Color code designations of CompactPCI connectors

The CompactPCI connectors use guide lugs in order to ensure proper connection. To avoid wiring errors, color coding is also used for the various standard operating voltages. The color coding prevents 5V peripheral cards from being mounted into the sockets designed for 3.3V voltage, and vice versa. The backplane connectors are always labeled in accordance with the signal voltage level (VIO).

Table 4-9: Color code designations of connectors

| Signal voltage                        | Color          |

|---------------------------------------|----------------|

| 3.3 V                                 | Cadmium yellow |

| 5 V                                   | Bright-blue    |

| Multipurpose board<br>(5 V and 3.3 V) | No             |

### 4.1.8.2 Pin assignment of CompactPCI XS20 and XS18 connectors

CPC507 is equipped with 2 CompactPCI bus connectors, where the pins have a pitch of  $2\times 2$  mm – XS20 and XS18.

#### Table 4-10: Assignment of pins of the CompactPCI XS20 (J1) system connector

| XS20 |     |          |          |          |          |          |     |

|------|-----|----------|----------|----------|----------|----------|-----|

| Pin  | z   | А        | В        | С        | D        | Е        | F   |

| 25   | GND | 5V       | REQ64#   | ENUM#    | 3.3V     | 5V       | GND |

| 24   | GND | AD[1]    | 5V       | LNG_VIO  | AD[0]    | ACK64#   | GND |

| 23   | GND | 3.3V     | AD[4]    | AD[3]    | LNG_5V   | AD[2]    | GND |

| 22   | GND | AD[7]    | GND      | LNG_3.3V | AD[6]    | AD[5]    | GND |

| 21   | GND | 3.3V     | AD[9]    | AD[8]    | M66EN    | C/BE[0]# | GND |

| 20   | GND | AD[12]   | GND      | VIO      | AD[11]   | AD[10]   | GND |

| 19   | GND | 3.3V     | AD[15]   | AD[14]   | LNG_GND  | AD[13]   | GND |

| 18   | GND | SERR#    | GND      | 3.3V     | PAR      | C/BE[1]# | GND |

| 17   | GND | 3.3V     | IPMB_SCL | IPMB_SDA | LNG_GND  | PERR#    | GND |

| 16   | GND | DEVSEL#  | GND      | VIO      | STOP#    | LOCK#    | GND |

| 15   | GND | 3.3V     | FRAME#   | IRDY#    | SHRT_GND | TRDY#    | GND |

| 14   | GND |          | ·        | -        | ·        |          | GND |

| 13   | GND | -        |          |          |          |          | GND |

| 12   | GND | -        |          |          |          |          | GND |

| 11   | GND | AD[18]   | AD[17]   | AD[16]   | LNG_GND  | C/BE[2]# | GND |

| 10   | GND | AD[21]   | GND      | 3.3V     | AD[20]   | AD[19]   | GND |

| 9    | GND | C/BE[3]# | SHRT_GND | AD[23]   | LNG_GND  | AD[22]   | GND |

| 8    | GND | AD[26]   | GND      | VIO      | AD[25]   | AD[24]   | GND |

| 7    | GND | AD[30]   | AD[29]   | AD[28]   | LNG_GND  | AD[27]   | GND |

| 6    | GND | REQ0#    | GND      | LNG_3.3V | CLK0     | AD[31]   | GND |

| 5    | GND | BRSVP1A5 | BRSVP1B5 | RST#     | LNG_GND  | GNT0#    | GND |

| 4    | GND | IPMB_PWR | HEALTHY# | LNG_VIO  | INTP     | INTS     | GND |

| 3    | GND | INTA#    | INTB#    | INTC#    | LNG_5V   | INTD#    | GND |

| 2    | GND | NC       | 5V       | NC       | NC       | NC       | GND |

| 1    | GND | 5V       | -12V     | NC       | +12V     | 5V       | GND |

| XS18 |     |           |           |           |          |           |     |

|------|-----|-----------|-----------|-----------|----------|-----------|-----|

| Pin  | z   | А         | В         | с         | D        | Е         | F   |

| 22   | GND | GA4       | GA3       | GA2       | GA1      | GA0       | GND |

| 21   | GND | CLK6      | GND       | RSV       | RSV      | RSV       | GND |

| 20   | GND | CLK5      | GND       | RSV       | GND      | RSV       | GND |

| 19   | GND | GND       | GND       | RSV       | RSV      | RSV       | GND |

| 18   | GND | BRSVP2A18 | BRSVP2B18 | BRSVP2C18 | GND      | BRSVP2E18 | GND |

| 17   | GND | BRSVP2A17 | GND       | PRST#     | REQ6#    | GNT6#     | GND |

| 16   | GND | BRSVP2A16 | BRSVP2B16 | DEG#      | GND      | BRSVP2E16 | GND |

| 15   | GND | BRSVP2A15 | GND       | FAL#      | REQ5#    | GNT5#     | GND |

| 14   | GND | AD[35]    | AD[34]    | AD[33]    | GND      | AD[32]    | GND |

| 13   | GND | AD[38]    | GND       | VIO       | AD[37]   | AD[36]    | GND |

| 12   | GND | AD[42]    | AD[41]    | AD[40]    | GND      | AD[39]    | GND |

| 11   | GND | AD[45]    | GND       | VIO       | AD[44]   | AD[43]    | GND |

| 10   | GND | AD[49]    | AD[48]    | AD[47]    | GND      | AD[46]    | GND |

| 9    | GND | AD[52]    | GND       | VIO       | AD[51]   | AD[50]    | GND |

| 8    | GND | AD[56]    | AD[55]    | AD[54]    | GND      | AD[53]    | GND |

| 7    | GND | AD[59]    | GND       | VIO       | AD[58]   | AD[57]    | GND |

| 6    | GND | AD[63]    | AD[62]    | AD[61]    | GND      | AD[60]    | GND |

| 5    | GND | C/BE[5]#  | GND       | VIO       | C/BE[4]# | PAR64     | GND |

| 4    | GND | VIO       | BRSVP2B4  | C/BE[7]#  | GND      | C/BE[6]#  | GND |

| 3    | GND | CLK4      | GND       | GNT3#     | REQ4#    | GNT4#     | GND |

| 2    | GND | CLK2      | CLK3      | SYSEN#    | GNT2#    | REQ3#     | GND |

| 1    | GND | CLK1      | GND       | REQ1#     | GNT1#    | REQ2#     | GND |

Table 4-11: Pin assignment of the XS18 (J2) system connector of 64-bit CompactPCI bus

### 4.1.8.3 I/O CompactPCI XS21, XS19, XS17 connectors (J3 - J5) and their pin assignment

In CPC507, part of the I/O signals are routed to the XS21, XS19 and XS17 connectors. A special backplane is required for using Rear I/O modules. The XS21, XS19 and XS17 connectors of the board are compatible with all standard 6U CompactPCI backplanes with I/O support through the corresponding connectors in the system slot.

The pin assignment of the XS21 (J3) connector complies with the PICMG 2.16 standard.

| XS21 |           |           |           |           |           |     |

|------|-----------|-----------|-----------|-----------|-----------|-----|

| Pin  | A         | В         | С         | D         | E         | F   |

| 1    | +VI/O     | PMC2_IO63 | PMC2_IO62 | PMC2_IO61 | PMC2_IO60 | GND |

| 2    | PMC2_IO59 | PMC2_IO58 | PMC2_IO57 | PMC2_IO56 | PMC2_IO55 | GND |

| 3    | PMC2_IO54 | PMC2_IO53 | PMC2_IO52 | PMC2_IO51 | PMC2_IO50 | GND |

| 4    | PMC2_IO49 | PMC2_IO48 | PMC2_IO47 | PMC2_IO46 | PMC2_IO45 | GND |

| 5    | PMC2_IO44 | PMC2_IO43 | PMC2_IO42 | PMC2_IO41 | PMC2_IO40 | GND |

| 6    | PMC2_IO39 | PMC2_IO38 | PMC2_IO37 | PMC2_IO36 | PMC2_IO35 | GND |

| 7    | PMC2_IO34 | PMC2_IO33 | PMC2_IO32 | PMC2_IO31 | PMC2_IO30 | GND |

| 8    | PMC2_IO29 | PMC2_IO28 | PMC2_IO27 | PMC2_IO26 | PMC2_IO25 | GND |

| 9    | PMC2_IO24 | PMC2_IO23 | PMC2_IO22 | PMC2_IO21 | PMC2_IO20 | GND |

| 10   | PMC2_IO19 | PMC2_IO18 | PMC2_IO17 | PMC2_IO16 | PMC2_IO15 | GND |

| 11   | PMC2_IO14 | PMC2_IO13 | PMC2_IO12 | PMC2_IO11 | PMC2_IO10 | GND |

| 12   | PMC2_IO9  | PMC2_IO8  | PMC2_IO7  | PMC2_IO6  | PMC2_IO5  | GND |

| 13   | PMC2_IO4  | PMC2_IO3  | PMC2_IO2  | PMC2_IO1  | PMC2_IO0  | GND |

| 14   | GND       | GND       | GND       | GND       | GND       | GND |

| 15   | ETH2_1+   | ETH2_1-   | GND       | ETH2_3+   | ETH2_3-   | GND |

| 16   | ETH2_0+   | ETH2_0-   | GND       | ETH2_2+   | ETH2_2-   | GND |

| 17   | ETH1_1+   | ETH1_1-   | GND       | ETH1_3+   | ETH1_3-   | GND |

| 18   | ETH1_0+   | ETH1_0-   | GND       | ETH1_2+   | ETH1_2-   | GND |

| 19   | GND       | GND       | GND       | GND       | GND       | GND |

Table 4-12: Pin assignment of the XS21 (J3) connector of CPC507

| XS19 |             |              |         |            |            |     |

|------|-------------|--------------|---------|------------|------------|-----|

| Pin  | Α           | В            | С       | D          | E          | F   |

| 1    | GND         | GND          | DP1_HPD | GND        | GND        | GND |

| 2    | DP1_LANE0+  | DP1_LANE0-   | GND     | NC         | LAN_LED0   | GND |

| 3    | DP1_LANE1+  | DP1_LANE1-   | GND     | NC         | LAN_LED1   | GND |

| 4    | DP1_LANE2+  | DP1_LANE2-   | GND     | NC         | LAN_LED2   | GND |

| 5    | DP1_LANE3+  | DP1_LANE3-   | GND     | NC         | LAN_LED3   | GND |

| 6    | DP1_AUX-    | DP1_AUX+     | GND     | NC         | NC         | GND |

| 7    | NC          | DP_CTRL_DAT  | GND     | GND        | GND        | GND |

| 8    | GND         | GND          | DP2_HPD | DP3_LANE0+ | DP3_LANE0- | GND |

| 9    | DP2_LANE0+  | DP2_LANE0-   | GND     | DP3_LANE1+ | DP3_LANE1- | GND |

| 10   | DP2_LANE1+  | DP2_LANE1-   | GND     | DP3_LANE2+ | DP3_LANE2- | GND |

| 11   | DP2_LANE2+  | DP2_LANE2-   | GND     | DP3_LANE3+ | DP3_LANE3- | GND |

| 12   |             |              |         |            |            | GND |

| 13   |             |              |         |            |            |     |

| 14   |             |              |         |            |            | GND |

| 15   | DP2_LANE3+  | DP2_LANE3-   | GND     | DP3_AUX-   | DP3_AUX+   | GND |

| 16   | DP2_AUX-    | DP2_AUX+     | GND     | GND        | GND        | GND |

| 17   | GND         | GND          | DP3_HPD | KBRST#     | USB_OC3    | GND |

| 18   | NC          | VDD_EN       | GND     | GND        | GND        | GND |

| 19   | NC          | LVDS_DDC_DAT | GND     | A20GATE    | HDA_SPKR   | GND |

| 20   | GND         | GND          | SDIN0   | NC         | HDA_RST#   | GND |

| 21   | HDA_SDOUT   | HDA_SDIN3    | GND     | GND        | GND        | GND |

| 22   | HDA_BIT_CLK | HDA_SYNC     | GND     | GPIO0      | GPIO3      | GND |

| 23   | NC          | RSTIN#       | +5V     | GPIO1      | GPIO4      | GND |

| 24   | GND         | GND          | +3.3V   | GPIO2      | GPIO5      | GND |

| 25   | NC          | NC           | NC      | GPIO6      | GPIO7      | GND |

Table 4-13: Assignment of the XS19 (J4) connector pins of the CPC507 module

| XS17 |            |           |           |           |           |     |

|------|------------|-----------|-----------|-----------|-----------|-----|

| Pin  | Α          | В         | С         | D         | E         | F   |

| 1    | LPC_AD0    | LPCCLK    | +3,3V     | +5V       | +5V       | GND |

| 2    | LPC_AD1    | SIOCLK    | +3,3V     | GND       | GND       | GND |

| 3    | LPC_AD2    | SUSCLK    | +3,3V     | USB1_DP   | USB1_DM   | GND |

| 4    | LPC_AD3    | SERIRQ    | +5V       | USB3_DP   | USB3_DM   | GND |

| 5    | LPC_FRAME# | LPC_RST#  | +5V       | USB0_DP   | USB0_DM   | GND |

| 6    | GND        | GND       | GND       | GND       | GND       | GND |

| 7    | ETH_MDI1+  | ETH_MDI1- | GND       | ETH_MDI3+ | ETH_MDI3- | GND |

| 8    | ETH_MDI0+  | ETH_MDI0- | GND       | ETH_MDI2+ | ETH_MDI2- | GND |

| 9    | GND        | GND       | GND       | GND       | GND       | GND |

| 10   | +VI/O      | PMC1_IO63 | PMC1_IO62 | PMC1_IO61 | PMC1_IO60 | GND |

| 11   | PMC1_IO59  | PMC1_IO58 | PMC1_IO57 | PMC1_IO56 | PMC1_IO55 | GND |